7 interrupt state vector, 7 interrupt state vector register (isvec) -10, Table 8-3. lin priority encoded interrupts -10 – Maxim Integrated MAXQ7667 User Manual

Page 140: Maxq7667 user’s guide, Table 8-3. lin priority encoded interrupts, 7 interrupt state vector register (isvec)

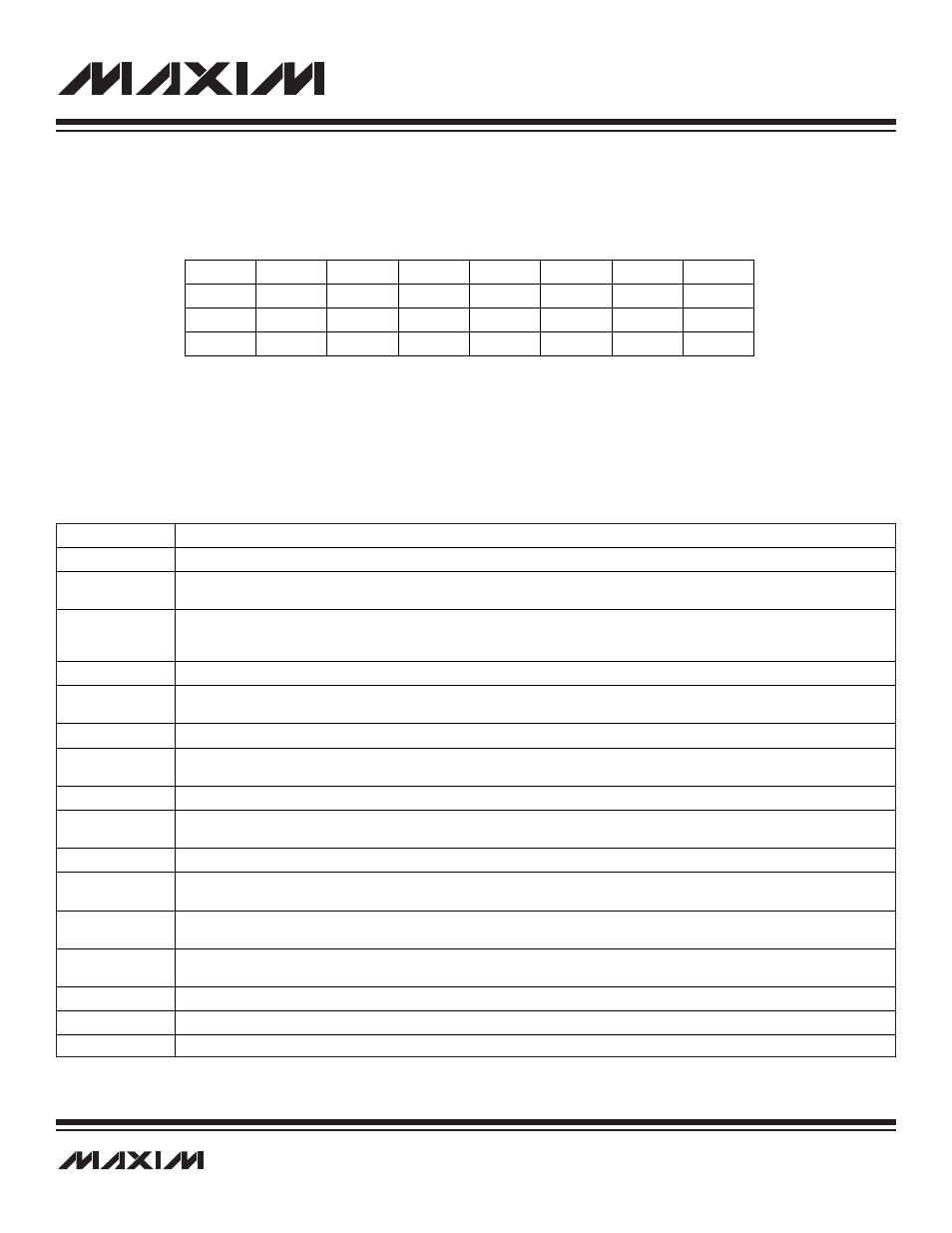

8.3.7 Interrupt State Vector Register (ISVEC)

Register Description:

Interrupt State Vector Register

Register Name:

ISVEC

Register Address:

Module 03h, Index 0Fh

Bits 7 to 4: Reserved.

Bits 3 to 0: Interrupt State Vector 3:0 (ISVEC[3:0]). This field is a priority encoded state vector that can be read by the host and used

as an index into an interrupt service routine table. If an interrupt is pending, the value in this field corresponds to the highest priority

pending interrupt. The state vector encoding is defined as shown in Table 8-3.

Table 8-3. LIN Priority Encoded Interrupts

__________________________________________________________________________________________________________

8-10

MAXQ7667 User’s Guide

ISVEC[3:0]

INTERRUPT STATUS

0

A wake-up request was detected on the LIN bus while the peripheral was in the low-power sleep mode.

1

Activity was detected on the LIN bus while the peripheral was in the low-power sleep state. This condition is only set if the PM bit

(CNT2.3) is set to 1.

2

In slave mode, this vector indicates that a header was received with a protected identifier that was within a valid range (i.e., an always

valid frame or one that passed the filter check specified by the IDFBH and IDFBL fields). In master mode, this vector indicates that the

protected identifier has been successfully transmitted.

3

Buffer overrun. This condition is set when a byte of data is received and there is no room in the receive FIFO.

4

Other communications error. This condition is set when a communication error occurs that is not explicitly assigned to another state

vector.

5

Reserved. This condition is never set.

6

Partial frame received successfully. This condition is set whenever the amount of data in the receive FIFO exceeds the threshold

configured by the RXFT[1:0] field (FCON.3:2).

7

Reserved. This condition is never set.

8

Complete frame received successfully. This condition is set when the last byte of a frame has been received and the checksum is

valid.

9

Reserved. This condition is never set.

10

Partial frame transmitted successfully. This condition is set whenever the amount of data in the transmit FIFO falls below the threshold

configured by the TXFT[1:0] field (FCON.5:4).

11

Complete frame transmitted successfully. This condition is set whenever the last byte of a frame has been transmitted and no errors

occurred on the bus during the transmission.

12

No master response. This condition is set if the peripheral is issuing wake-up requests on the bus and there is no response from the

master.

13

No bus activity. This condition is set if the bus is idle for a period of more than 4 seconds.

14

Reserved. This condition is never set.

15

No pending interrupt. This condition is set when there are no pending interrupts.

r = read

Note: ISVEC is cleared to 0Fh on all forms of reset.

Bit #

7

6

5

4

3

2

1

0

Name

—

—

—

—

ISVEC3

ISVEC2

ISVEC1

ISVEC0

Reset

0

0

0

0

1

1

1

1

Access

r

r

r

r

r

r

r

r