2 schedule timer registe, 3 schedule alarm registe, 2 schedule timer register (stim) -4 – Maxim Integrated MAXQ7667 User Manual

Page 129: 3 schedule alarm register (salm) -4, Maxq7667 user’s guide, 2 schedule timer register (stim), 3 schedule alarm register (salm)

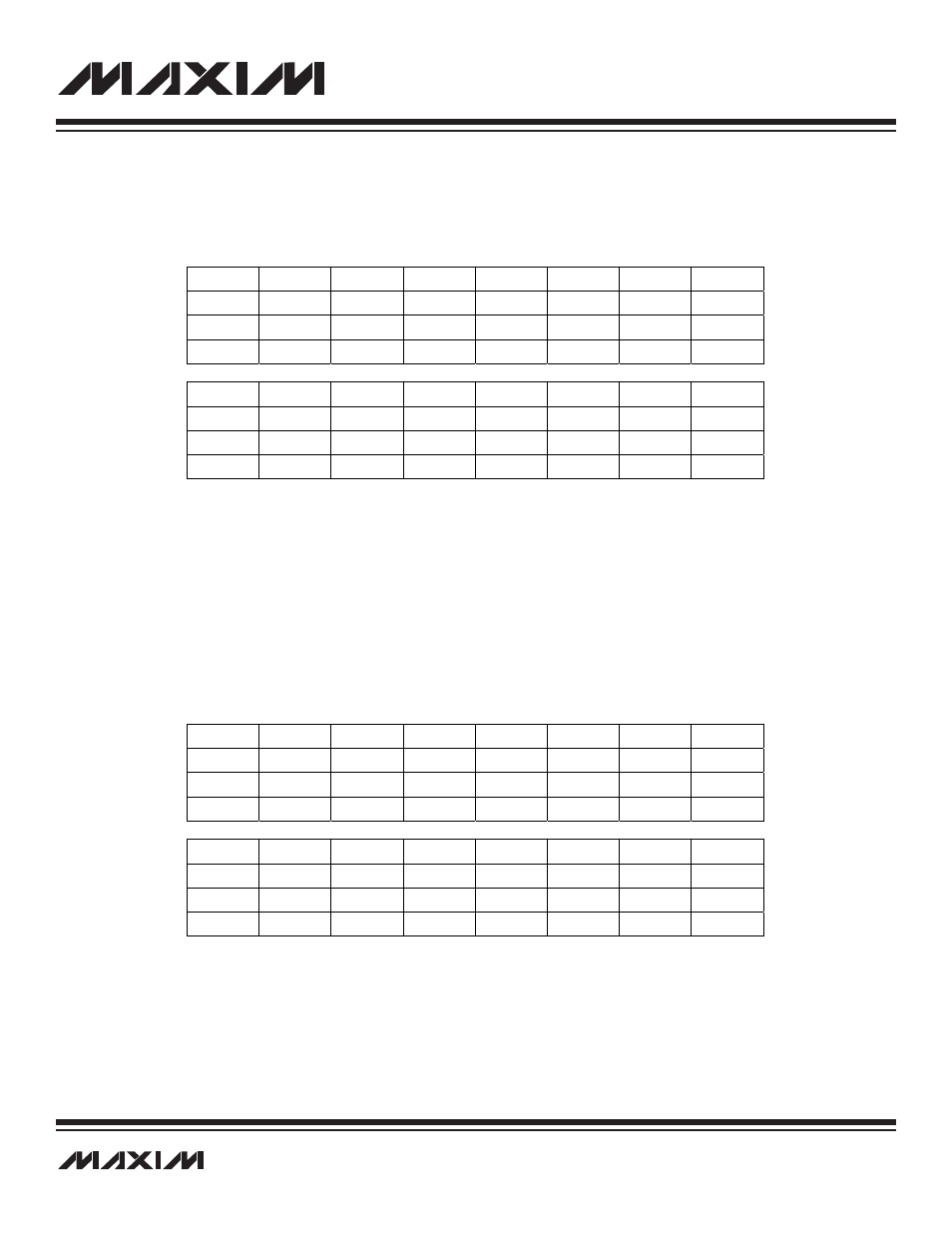

7.2.2 Schedule Timer Register (STIM)

Register Description:

Schedule Timer Register

Register Name:

STIM

Register Address:

Module 01h, Index 0Fh

Bits 15 to 0: Schedule Timer Register Bits 15:0 (STIM[15:0]). When STIME is 1, STIM increases by 1 every prescaled system clock,

and is automatically cleared to 0 when any one of the following conditions happens:

1)

SSYNC_EN is 1 and an external synchronization event occurs.

2)

SALME is 1 and STIM equals SALM. (Note that SALMF is set to 1 in this case.)

7.2.3 Schedule Alarm Register (SALM)

Register Description:

Schedule Alarm Register

Register Name:

SALM

Register Address:

Module 01h, Index 10h

Bits 15 to 0: Schedule Alarm Register Bits 15:0 (SALM[15:0]). This register holds the value of the schedule alarm.

___________________________________________________________________________________________________________

7-4

MAXQ7667 User’s Guide

Bit #

15

14

13

12

11

10

9

8

Name

STIM15

STIM14

STIM13

STIM12

STIM11

STIM10

STIM9

STIM8

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

Bit #

7

6

5

4

3

2

1

0

Name

STIM7

STIM6

STIM5

STIM4

STIM3

STIM2

STIM1

STIM0

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

r = read, w = write

Note: This register is cleared to 00h on all forms of reset.

Bit #

15

14

13

12

11

10

9

8

Name

SALM15

SALM14

SALM13

SALM12

SALM11

SALM10

SALM9

SALM8

Reset

0

0

0

0

0

0

0

0

Access

r

r

r

r

r

r

r

r

Bit #

7

6

5

4

3

2

1

0

Name

SALM7

SALM6

SALM5

SALM4

SALM3

SALM2

SALM1

SALM0

Reset

0

0

0

0

0

0

0

0

Access

r

r

r

r

r

r

r

r

r = read (This register is writable when either STIME or SALME is 1.)

Note: This register is cleared to 00h on all forms of reset.