Table 8-2. serial port operating modes -6, Maxq7667 user’s guide, Table 8-2. serial port operating modes – Maxim Integrated MAXQ7667 User Manual

Page 136

Bit 5: Serial Port Mode Bit 2 (SM2). The function of this bit is dependent on the operating mode of the serial port. In mode 0, it deter-

mines the speed of the serial clock signal (either 1/4 or 1/12 the system clock rate). In mode 1, setting this bit to 1 disables the receive

interrupt if an invalid stop bit is received. In modes 2 and 3, setting this bit to 1 prevents the receive interrupt from being set if the 9th

received bit is a 0.

SM2 = 0: clock is divided by 12

SM2 = 1: clock is divided by 4

Bit 4: Receive Enable (REN). In legacy UART mode, this bit enables the receiver. In LIN master or LIN slave mode, the receiver is

controlled by the LIN protocol state machine and this bit serves no purpose.

Bit 3: 9th Transmission Bit State (TB8). In legacy UART mode, the host writes this bit to reflect the state of the 9th transmitted bit. If

the FIFO is enabled, the host must set this bit to the correct state before writing to the SBUF register. This bit serves no purpose in LIN

master or LIN slave mode.

Bit 2: 9th Received Bit State (RB8). In legacy UART mode, this bit is written by the peripheral to reflect the state of the 9th received

bit. If the FIFO is enabled, the host must read the SBUF register before reading this bit. This bit serves no purpose in LIN master or LIN

slave mode.

Bit 1: Transmit Interrupt Flag (TI). In legacy UART mode, this bit is set by the peripheral to indicate that a transmit interrupt condi-

tion occurred. If the FIFO is enabled, this bit is set when the amount of data in the FIFO falls below the threshold determined by the

TXFT[1:0] field (FCON.5:4). If the FIFO is disabled, this flag is set every time a byte has been transmitted. This bit serves no purpose

in LIN master or LIN slave mode.

Bit 0: Receive Interrupt Flag (RI). In legacy UART mode, the peripheral sets this bit to indicate that a receive interrupt condition

occurred. If the FIFO is enabled, it is set when the amount of data in the receive FIFO exceeds the threshold determined by the

RXFT[1:0] field (FCON.3:2). If the FIFO is disabled, this bit is set every time a byte is received. This bit serves no purpose in LIN mas-

ter or LIN slave mode.

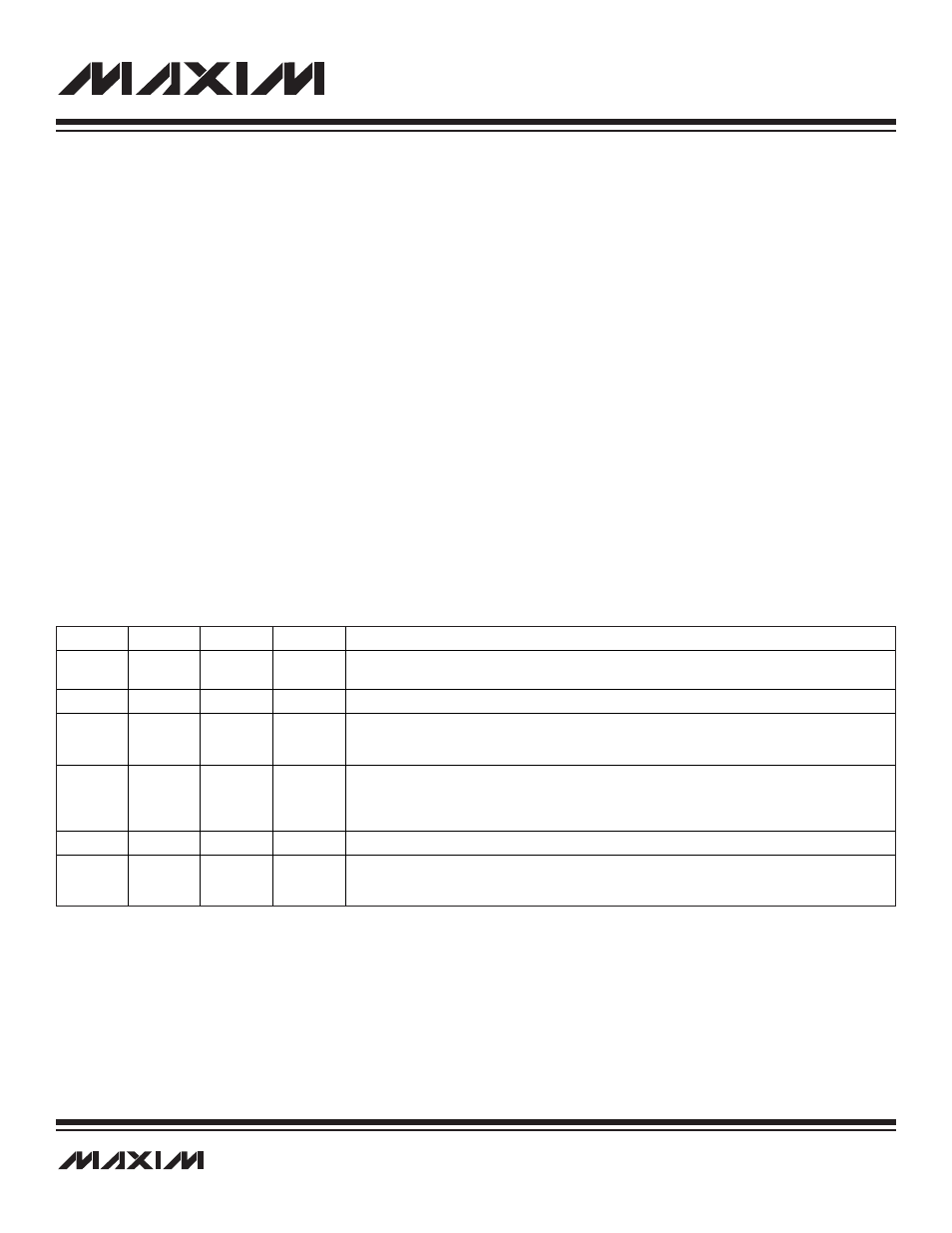

Table 8-2. Serial Port Operating Modes

___________________________________________________________________________________________________________

8-6

MAXQ7667 User’s Guide

MODE

SM0

SM1

SM2

FUNCTION

0

0

0

0

Synchronous communication (mode 0). The peripheral transmits and receives 8-bit data using a

synchronous protocol. The clock rate is 1/12 the system clock rate.

0

0

0

1

Same as above, except the clock rate is 1/4 the system clock rate.

1

0

1

X

Asynchronous communication (mode 1). The peripheral transmits and receives 8-bit data using an

asynchronous protocol with one start bit and one stop bit. In this mode, the on-chip baud-rate

generator determines the communication speed.

2

1

0

0

Asynchronous communication (mode 2). The peripheral transmits and receives 9-bit data using an

asynchronous protocol with one start bit and one stop bit. In this mode, the communication speed is

either 1/32 or 1/64 the system clock rate, depending on the state of the SMOD bit (SMD.1). Automatic

address recognition (legacy multiprocessor communication) is disabled.

2

1

0

1

Same as above, except the automatic address recognition is enabled.

3

1

1

X

This is the same as mode 2, except the communication speed is determined by the baud-rate

generator. Automatic address recognition (legacy multiprocessor communication) is enabled when

SM2 = 1.