1 accumulator pointer re, 2 accumulator pointer co, 1 accumulator pointer register (ap) -6 – Maxim Integrated MAXQ7667 User Manual

Page 50: 2 accumulator pointer control register (apc) -6, Maxq7667 user’s guide, 1 accumulator pointer register (ap), 2 accumulator pointer control register (apc)

___________________________________________________________________________________________________________

4-6

MAXQ7667 User’s Guide

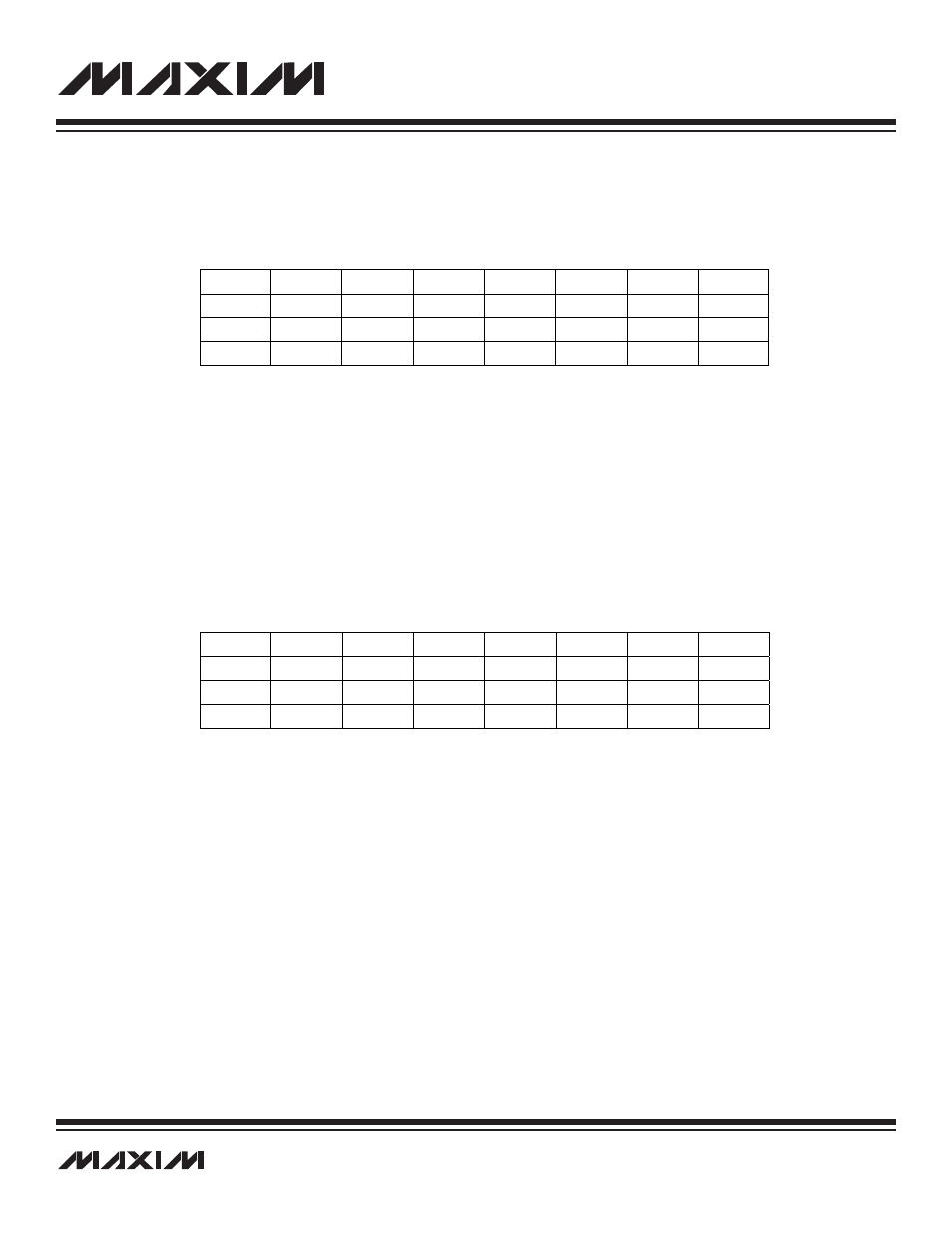

4.1.1 Accumulator Pointer Register (AP)

Register Description:

Accumulator Pointer Register

Register Name:

AP

Register Address:

Module 08h, Index 00h

Bits 7 to 4: Reserved. Read 0, write ignored.

Bits 3 to 0: Accumulator Select 3:0 (AP[3:0]). These bits select which of the 16 accumulator registers are used for arithmetic and

logical operations. If the APC register has been set to perform automatic increment/decrement of the active accumulator, this setting

will be automatically changed after each arithmetic or logical operation. If a MOVE AP, Acc instruction is executed, any enabled AP

inc/dec/modulo control will take precedence over the transfer of Acc data into AP.

4.1.2 Accumulator Pointer Control Register (APC)

Register Description:

Accumulator Pointer Control Register

Register Name:

APC

Register Address:

Module 08h, Index 01h

Bit 7: Accumulator Pointer Clear (CLR). Writing this bit to 1 clears the accumulator pointer AP to 0. Once set, this bit will automati-

cally be reset to 0 by hardware. If a MOVE APC, Acc instruction is executed requesting that AP be set to 0 (i.e., CLR = 1), the AP clear

function overrides any enabled inc/dec/modulo control. All reads from this bit return 0.

Bit 6: Accumulator Pointer Increment/Decrement Select (IDS). If this bit is set to 0, the accumulator pointer AP is incremented fol-

lowing each arithmetic or logical operation according to MOD[2:0]. If this bit is set to 1, the accumulator pointer AP is decremented

following each arithmetic or logical operation according to MOD[2:0]. If MOD[2:0] is set to 000, the setting of this bit is ignored.

Bits 5 to 3: Reserved. Read 0, write ignored.

Bit #

7

6

5

4

3

2

1

0

Name

—

—

—

—

AP3

AP2

AP1

AP0

Reset

0

0

0

0

0

0

0

0

Access

r

r

r

r

rw

rw

rw

rw

r = read, w = write

Note: This register is cleared to 00h on all forms of reset.

Bit #

7

6

5

4

3

2

1

0

Name

CLR

IDS

—

—

—

MOD2

MOD1

MOD0

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

r

r

r

rw

rw

rw

r = read, w = write

Note: This register is cleared to 00h on all forms of reset.