3 oscillator control re, 4 system clock control, 3 oscillator control register (oscc) -6 – Maxim Integrated MAXQ7667 User Manual

Page 258: 4 system clock control register (ckcn) -6, Maxq7667 user’s guide, 3 oscillator control register (oscc), 4 system clock control register (ckcn)

__________________________________________________________________________________________________________

15-6

MAXQ7667 User’s Guide

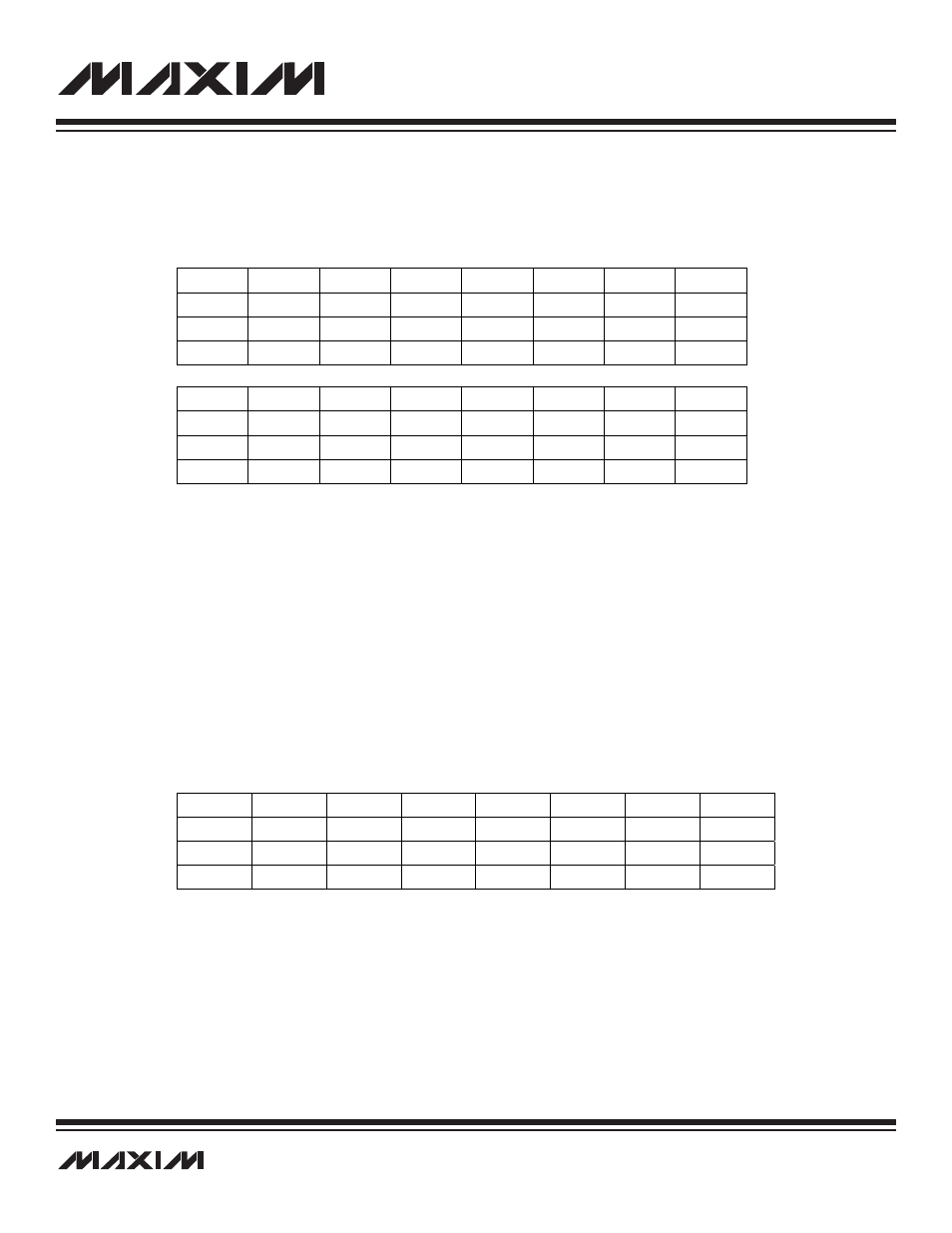

15.2.3 Oscillator Control Register (OSCC)

Register Description:

Oscillator Control Register

Register Name:

OSCC

Register Address:

Module 05h, Index 0Bh

Bits 15 to 4: Reserved. Read returns 0.

Bits 3 and 2: SAR ADC Clock Divider (SARCD[1:0]). See Section 14 for details on this bit.

Bit 1: Crystal Enable (XTE). Forces the XTAL oscillator to be enabled. When this bit is set to 0, the XTAL oscillator powers on and off

as required by the clock selection XTRC (CKCN.7). Setting this bit forces the XTAL oscillator to remain on even when it is not being

used. By setting this bit, the XTAL remains warm, and source clock switches via XTRC (CKCN.7) will not require a crystal warmup time.

Bit 0: RC Oscillator Enable (RCE). Forces the RC oscillator to be enabled. When this bit is set to 0, the RC oscillator powers on and

off as required by the clock selection XTRC (CKCN.7), use of the watchdog, or flash program/erase cycles. Setting this bit to 1 forces

the RC to remain on at all times.

15.2.4 System Clock Control Register (CKCN)

Register Description:

System Clock Control Register

Register Name:

CKCN

Register Address:

Module 08h, Index 0Eh

Bit 7: External Crystal Select (XTRC). This bit selects the external oscillator/crystal or internal RC oscillator as the desired clock

source. The XTRC bit will be inverse of RCMD except during the crystal warmup period when resuming from the stop mode through

the RC oscillator. This bit is cleared to 0 after a power-on/brownout reset, which selects the internal RC oscillator as the clock source;

otherwise, it is unchanged by other forms of reset. Changing the XTRC bit from 0 to 1 causes the system clock source to swap from

RC to crystal oscillator. This change occurs automatically within a few clock cycles if sufficient crystal warmup time has elapsed since

the XTE bit of the OSCC register was set. If the crystal has not finished warming up when XTRC is set to 1, the crystal oscillator con-

tinues to warm up and the clock source swaps to crystal when this is complete. The XTRDY bit of the ASR register indicates when the

crystal oscillator circuit is ready (XTRDY = 1), and the clock source can swap from RC oscillator to crystal.

Bit #

15

14

13

12

11

10

9

8

Name

—

—

—

—

—

—

—

—

Reset

0

0

0

0

0

0

0

0

Access

r

r

r

r

r

r

r

r

Bit #

7

6

5

4

3

2

1

0

Name

—

—

—

—

SARCD1

SARCD0

XTE

RCE

Reset

0

0

0

0

0

0

0

1

Access

r

r

r

r

r

r

r

r

r = read. (Note that some clock control bits may have locking mechanisms for write.)

Note: OSCC is cleared to 0001h on reset.

Bit #

7

6

5

4

3

2

1

0

Name

XTRC

—

RCMD

STOP

SWB

PMME

CD1

CD0

Reset

0

0

0

0

0

0

0

0

Access

rw

r

r

rw

rw

rw

rw

rw

r = read, w = write (There is a locking mechanism for the PMME, CD1, and CD0 bits when changing their bit values.)

Note: Bits 5:0 are cleared to 0 on all forms of reset. Bits 6 and 7 are cleared to 0 by a power-on reset only.