3 schedule timer operation, 3 schedule timer operation -5, Maxq7667 user’s guide – Maxim Integrated MAXQ7667 User Manual

Page 130

7.3 Schedule Timer Operation

The MAXQ7667 has a schedule timer that can be used for general timekeeping and interval alarms and wake-up alarms. The timer is

a 16-bit up-counter that is incremented by the system clock after the system clock has been divided by a prescaler. The counter value

is read through the STIM register. Writing to the STIM register sets the counter to the written value.

The divisor used in the system clock prescaler is set by STDIV and divides the system clock by one of the following values: 1, 2, 4, 8,

16, 32, 64, or 128. Table 7-1 shows the STDIV setting used to select each divisor. When operating with a 16MHz system clock, the

prescaler provides full-scale timer values that range from 4.096ms [(1/16MHz) x 1 x 65,536] to 524ms [(1/16MHz) x 128 x 65,536]. If

measurement times longer than 524ms are needed, a software counter can be used to tally the number of times the schedule timer

has alarmed or rolled over. This technique can be expanded to accommodate any desired length of time.

7-5

___________________________________________________________________________________________________________

MAXQ7667 User’s Guide

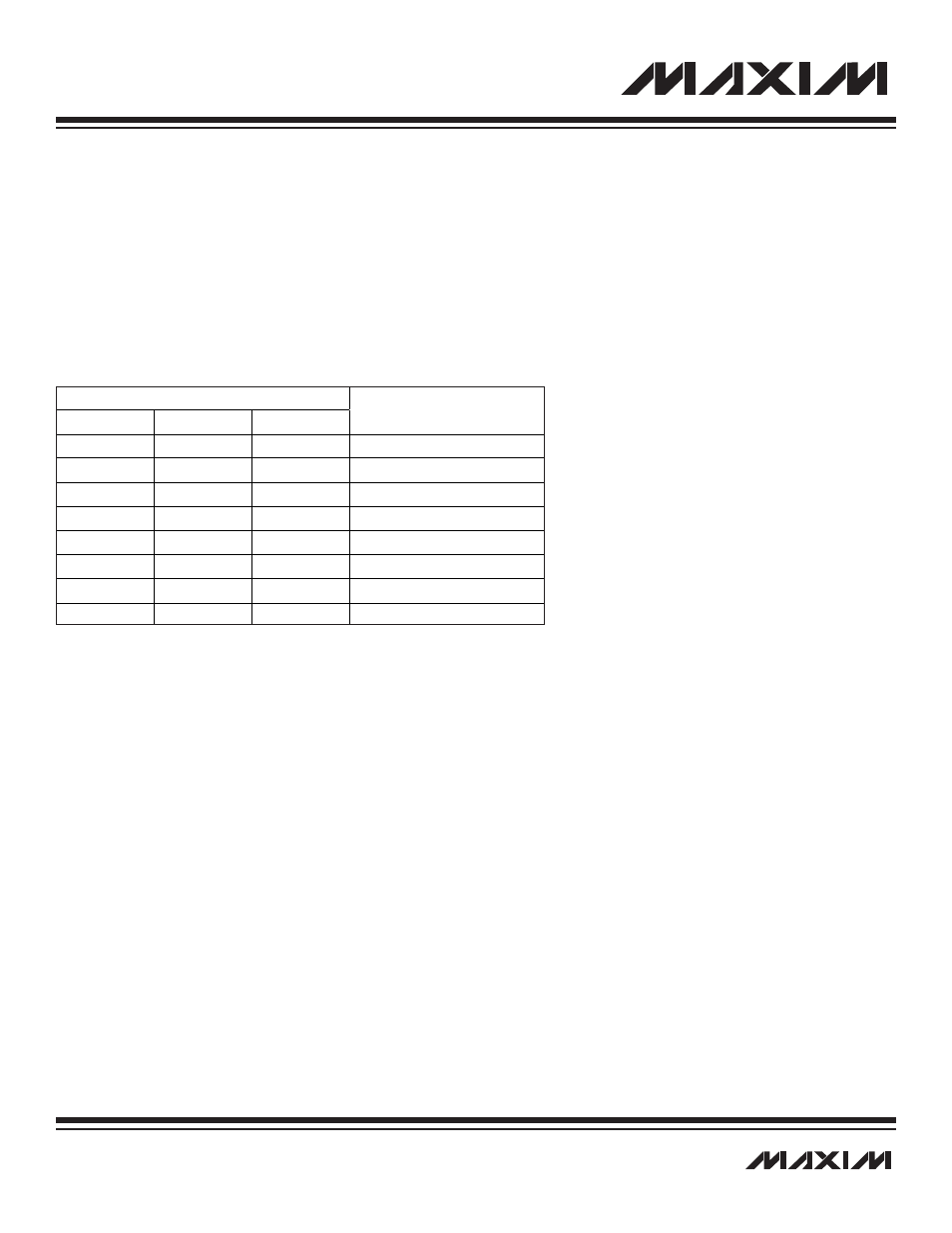

Table 7-1. STDIV Setting to Select the SYSCLK Divisor

The usefulness of the schedule timer is increased by its alarm feature. If enabled (SALME = 1 and STIME = 1), an alarm event is initi-

ated when STIM = SALM. The alarm event sets the alarm flag, SALMF; resets STIM to 0; and generates an interrupt if enabled. The

alarm interrupt is enabled by setting the SALIE bit to 1. It is also important that the module interrupt, IMR1, and the global interrupt,

IGE, are also enabled for the interrupt event to occur successfully.

The schedule timer, alarm value, alarm flag, and all the enable bits are cleared to zero by all forms of reset.

The schedule timer can be synchronized to an external event through pin P1.7/SYNC. This is the only external pin that is directly asso-

ciated with the schedule timer. When enabled (SSYNC_EN = 1), a low-to-high transition on P1.7/SYNC causes the next system clock

to clear the timer. The signal on P1.7/SYNC must remain high for at least one system clock cycle. After being high for one clock cycle,

P1.7/SYNC can remain high or be taken low again. Synchronizing the schedule timers on multiple MAXQ7667s is useful when trian-

gulation is used to locate a target’s position.

When switchback is enabled (see Section 15), the interrupt from schedule timer is a valid source to switch out of the stop mode.

STDIV[2:0]

2

1

0

PRESCALE DIVIDER

0

0

0

1

0

0

1

2

0

1

0

4

0

1

1

8

1

0

0

16

1

0

1

32

1

1

0

64

1

1

1

128