2 breakpoint register, 2 breakpoint register 4 (bp4) -13, Maxq7667 user’s guide – Maxim Integrated MAXQ7667 User Manual

Page 211

12-13

_________________________________________________________________________________________________________

MAXQ7667 User’s Guide

12.3.2.2 Breakpoint Register 4 (BP4)

Register Description:

Breakpoint Register 4

Register Name:

BP4

This register is accessible only via background mode read/write commands.

When (REGE = 0): This register serves as one of the two data memory address breakpoints. When DME is set in background mode,

the debug engine monitors the data memory address bus activity while the CPU is executing the user program. If an address match

is detected, a break occurs, allowing the debug engine to take over control of the CPU and enter debug mode.

When (REGE = 1): This register serves as one of the two register breakpoints. A break occurs when the destination register address

for the executed instruction matches with the specified module and index. When used as register breakpoint, the bits BP4[3:0] are rec-

ognized as module specifier and bits BP4[8:4] are recognized as the register index within the module. The bits BP4[15:9] are ignored.

This register defaults to FFFFh after a power-on reset or test-logic-reset TAP state.

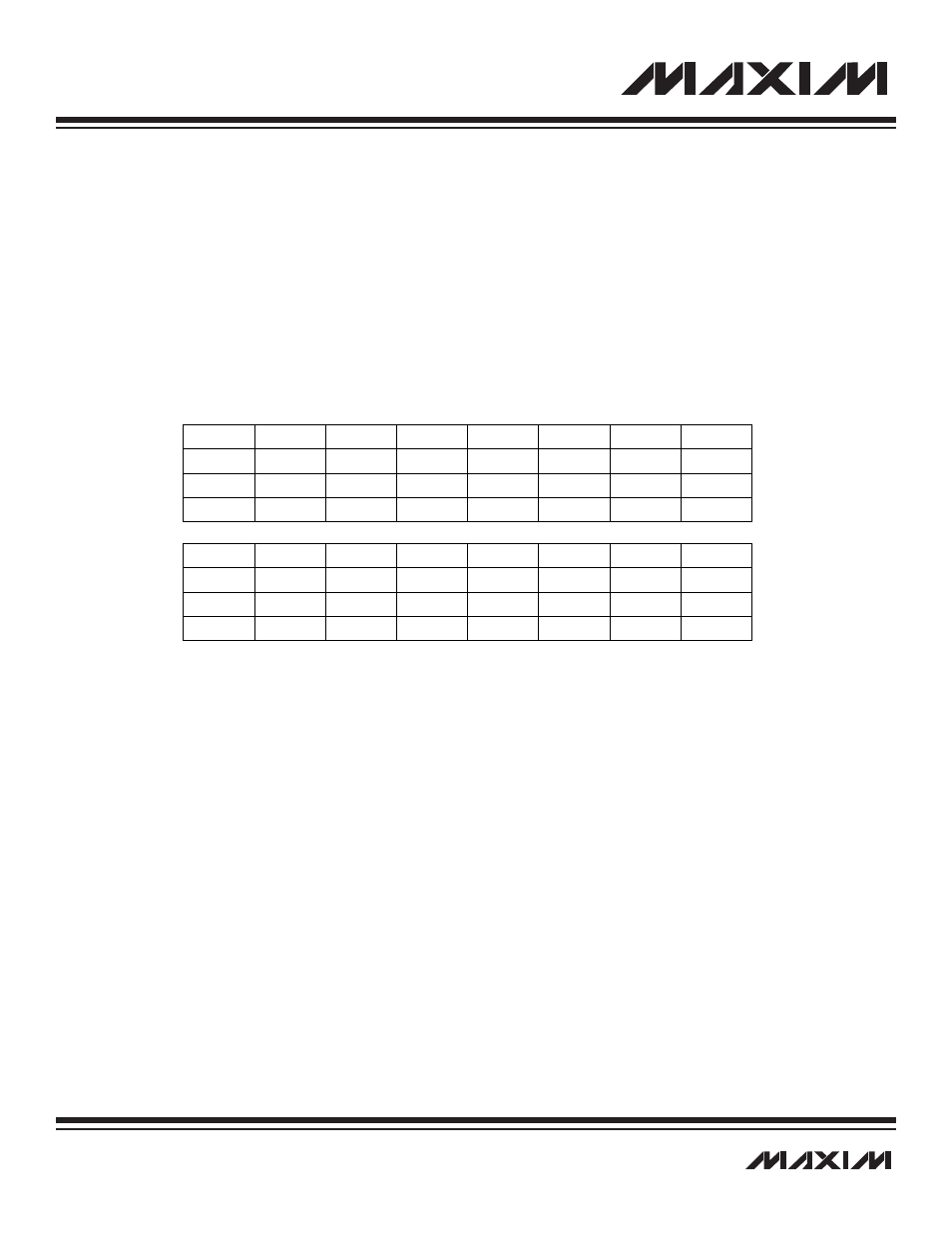

Bits 15 to 0: Breakpoint Register 4 Bits 15:0 (BP4[15:0])

Bit #

15

14

13

12

11

10

9

8

Name

BP415

BP414

BP413

BP412

BP411

BP410

BP49

BP48

Reset

1

1

1

1

1

1

1

1

Access

s

s

s

s

s

s

s

s

Bit #

7

6

5

4

3

2

1

0

Name

BP47

BP46

BP4 5

BP44

BP43

BP42

BP41

BP40

Reset

1

1

1

1

1

1

1

1

Access

s

s

s

s

s

s

s

s

s = special (accessible only by background mode read/write commands)