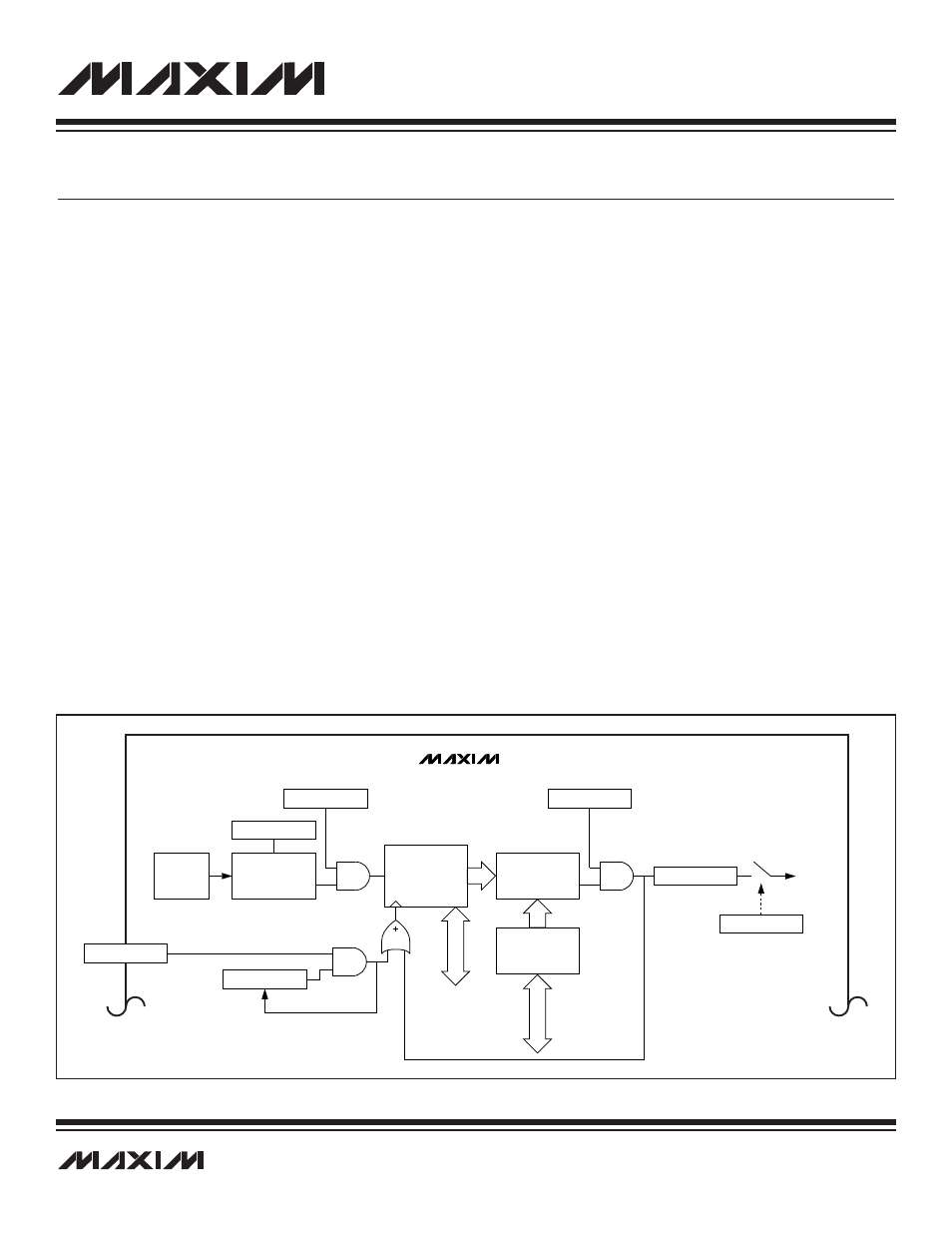

1 architecture, 1 architecture -2, Figure 7-1. schedule timer module block diagram -2 – Maxim Integrated MAXQ7667 User Manual

Page 127: Maxq7667 user’s guide

___________________________________________________________________________________________________________

7-2

MAXQ7667 User’s Guide

SECTION 7: SCHEDULE TIMER

The MAXQ7667’s schedule timer is a much simpler implementation of the real-time clock module found in many MAXQ microcon-

trollers. The schedule timer provides a means for general timekeeping and software synchronization to the external I/O.

The schedule timer features include the following:

• 16-bit autoreload up-counter for the timer

• Programmable 16-bit alarm register

• Alarm interrupts

• Schedule timer is incremented by a prescaled system clock (SYSCLK, see Section 15). The system clock can be prescaled to 1,

2, 4, 8, 16, 32, 64, and 128.

• Schedule timer up-counter can be reset through an external I/O pin, thus allowing synchronization of the schedule timer to an

external event.

• Wake-up alarm to pull the system clock from stop mode to normal operation (divide-by-1)

7.1 Architecture

The MAXQ7667 implements the following features:

• A 16-bit counter (STIM), clocked by a divided-down version of SYSCLK. Software can read/write STIM to access/modify the time-

stamp. STIM is enabled by SCNT.0:STIME.

• A16-bit alarm register (SALM). It is readable/writable from software. When STIM equals SALM, interrupts can be generated to

CPU. SALM is enabled by SCNT1:SALME.

Note: SALM is writable by software ONLY when either STIME or SALME is 0.

• STIM is cleared to 0 by hardware when one of the following conditions occurs:

1) STIM wraps around from FFFFh to 0.

2) STIM equals SALM and the alarm function is enabled (i.e., SALME = 1). (Note that when SCNT.6:SALMF is set to 1, an inter-

rupt is generated.)

3) An external rising-edge synchronization event from input pad P1.7 and is enabled by SCNT.8:SSYNC_EN. SSYNC_EN clears

when such an event occurs.

PROGRAMMABLE

DIVIDE BY

1, 2, 4, ..., 128

COMPARATOR

STIM = SALM

SALM

REGISTER

S

A

L

M

[1

5

:0

]

STIM

16-BIT UP

COUNTER

SCNT.11:STDIV

SCNT.0:STIME

CLR

CLR

SCHEDULE TIMER

SYSTEM

CLOCK

MAXQ7667

SCNT.8:SSYNC_EN

SCNT.11:SALIE

SCNT.1:SALME

INT

AN INTERRUPT IS

GENERATED WHEN

SALIE = 1 AND

SALMF = 1

SCNT.6:SALMF

S

T

IM

[1

5

:0

]

P1.7/SYNC

Figure 7-1. Schedule Timer Module Block Diagram