2 write collision flag, 3 mode fault flag (modf), 3 spi interrupts – Maxim Integrated MAXQ7667 User Manual

Page 178: 2 write collision flag (wcol) -16, 3 mode fault flag (modf) -16, 3 spi interrupts -16, Figure 9-6. maxq interrupt enabling scheme -16, Maxq7667 user’s guide, 2 write collision flag (wcol)

__________________________________________________________________________________________________________

9-16

MAXQ7667 User’s Guide

9.2.2 Write Collision Flag (WCOL)

A write collision occurs if a write to the SPIB data register is attempted during a transfer cycle. The MAXQ7667’s write path is a single-

buffered path with the shift register acting as both the write buffer and shift register. If the STBY flag is set (1), this marks that a trans-

fer cycle is in progress. Any writes to the SPIB with STBY set are blocked to maintain the integrity of the shift register contents. The

transfer cycle in progress is completed normally. But the WCOL bit is set (1), marking an error condition. When a write collision is

detected, the error-handling routine should clear the WCOL bit. The WCOL flag is set by the SPI port module but must be cleared by

writing a 0 to this bit or by any reset condition.

9.2.3 Mode Fault Flag (MODF)

The MODF detects if the SS line is asserted on the MAXQ7667 when the SPI port is configured as an SPI bus master. In the SPI port

protocol, the master device handles control of the SS line to enable target slave devices for SPI transfers. When more than one SPI

master is on the bus this bus clash condition can occur. To enable mode-fault detection, the mode fault enable (MODFE) must be set

(1). When the SS pin is asserted (0) while the SPI port is in master mode, the MODF flag is set and the following occurs:

1) The master MSTM bit is cleared (0) to reconfigure the device as a slave.

2) The SPIEN bit is cleared (0), disabling the SPI port.

3) The mode fault flag (MODF) is set (1).

The MODF flag is set by the SPI port module but must be cleared by writing a 0 to this bit or by any reset condition.

9.3 SPI Interrupts

The SPI port has four flags that generate interrupts to the µC:

•

SPI Transfer Complete Flag (SPIC)

•

Receive Overrun Flag (ROVR)

•

Write Collision Flag (WCOL)

•

Mode Fault Flag (MODF)

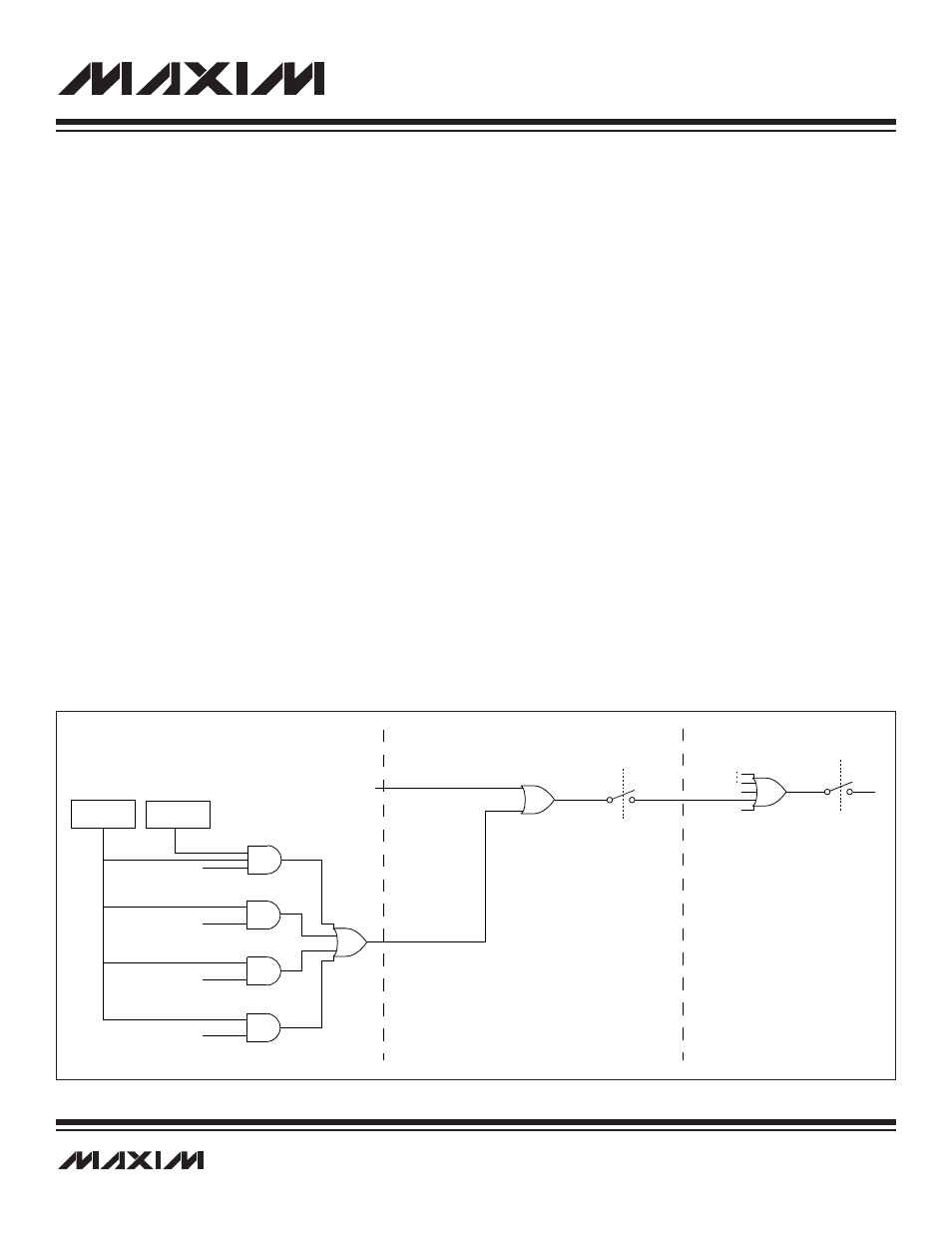

All the flags can be enabled to generate an interrupt by using the enable SPI interrupts (ESPII) bit (Figure 9-6). The MODF has an addi-

tional enable called the mode-fault-enable bit that must be set (1) to enable mode-fault detection.

All status flags must be cleared in the interrupt service routine by writing a 0 to them, or on any form of reset. Clearing the ESPII bit

disables the interrupts but does not clear the underlying error flag condition or the status flag.

Figure 9-6. MAXQ Interrupt Enabling Scheme

GLOBAL INTERRUPT

MASK ENABLE

(IGE)

INTERRUPT MASK

MODULE 1 ENABLE

(IMR.1)

SCHEDULE TIMER/ALARM

ESPII

MODFE

MODF

WCOL

ROVR

SPIC

SPI INTERRUPT

MOD2

GLOBAL INTERRUPTS

MODULE INTERRUPTS

LOCAL INTERRUPTS

SPI PORT

MOD0