2 in-system programming p, 1 in-circuit debug flag, 2 in-system programming peripheral registers -3 – Maxim Integrated MAXQ7667 User Manual

Page 221: 1 in-circuit debug flag register (icdf) -3, Table 13-1. programming source select decode -3, Maxq7667 user’s guide, 2 in-system programming peripheral registers, Table 13-1. programming source select decode, 1 in-circuit debug flag register (icdf)

13-3

__________________________________________________________________________________________________________

MAXQ7667 User’s Guide

13.2 In-System Programming Peripheral Registers

The MAXQ7667 in-system programming peripheral registers are described here. It is also possible for the MAXQ7667 to bootstrap itself

into in-system programming mode by setting the proper bits in the in-circuit debug flag register (ICDF) and invoking a reset. The pro-

cedure for invoking in-system programming in this manner must be defined and supported by the application firmware as discussed

in Section 13.5 and Section 13.6.

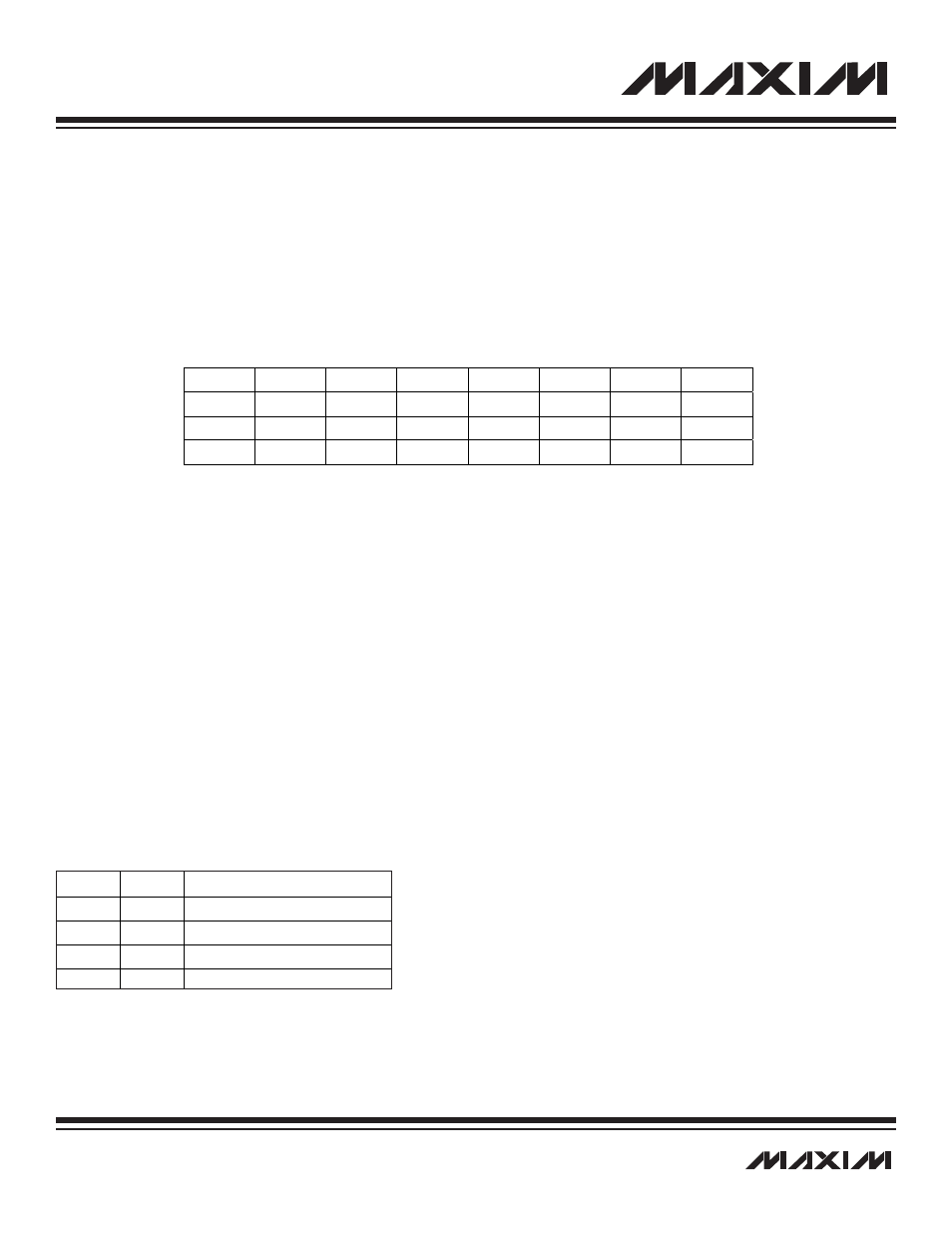

13.2.1 In-Circuit Debug Flag Register (ICDF)

Register Description:

In-Circuit Debug Flag Register

Register Name:

ICDF

Register Address:

Module 02h, Index 1Bh

Bits 7 to 4: Reserved.

Bits 3 and 2: Programming Source Select Bits 1 and 0 (PSS[1:0]). These bits are used to select a programming interface during in-

system programming when SPE is set to logic 1. Otherwise, the logic values of these bits have no meaning. The logical states of these

bits, when read by the CPU, reflect the logical-OR of the PSS bits that are write accessible by the CPU and those in the system pro-

gramming buffer register (SPB) of the TAP module (which are accessible via JTAG). These bits are read/write accessible by the CPU

and are cleared to 0 by a power-on reset or test-logic-reset (see Section 11). CPU writes to the PSS bits result in clearing of the JTAG

PSS[1:0] bits, as shown in Table 13-1.

Bit 1: System Program Enable (SPE). This bit controls the behavior of the MAXQ7667 following a reset. The SPE bit is used for in-

system programming support, and its logical state, when read by the CPU, always reflects the logical-OR of the SPE bit that is write

accessible by the CPU and the SPE bit of the SPB register in the TAP module, which is accessible via JTAG. The logical state of this

bit determines the program flow after a reset.

0 = The MAXQ7667 jumps to application code in flash at 0000h following a reset.

1 = The MAXQ7667 executes the in-system programming bootloader following a reset.

This bit allows read/write access by the CPU and is cleared to 0 only on a power-on reset or test-logic-reset (see Section 11). The JTAG

SPE bit is cleared by hardware when the ROD bit is set. CPU writes to the SPE bit result in clearing of the JTAG PSS[1:0] bits.

Bit 0: Serial Transfer Complete (TXC). See Section 12 for more information on this bit.

Table 13-1. Programming Source Select Decode

PSS1

PSS0

PROGRAMMING SOURCE

0

0

JTAG

0

1

UART

1

0

Reserved

1

1

Reserved

Bit #

7

6

5

4

3

2

1

0

Name

—

—

—

—

PSS1

PSS0

SPE

TXC

Reset

0

0

0

0

0

0

0

0

Access

r

r

r

r

rw

rw

rw

rw

r = read, w = write