25 frame pointer registe, 26 data pointer 0 regist, 25 frame pointer register (fp) -20 – Maxim Integrated MAXQ7667 User Manual

Page 64: 26 data pointer 0 register (dp[0]) -20, Maxq7667 user’s guide, 25 frame pointer register (fp), 26 data pointer 0 register (dp[0])

__________________________________________________________________________________________________________

4-20

MAXQ7667 User’s Guide

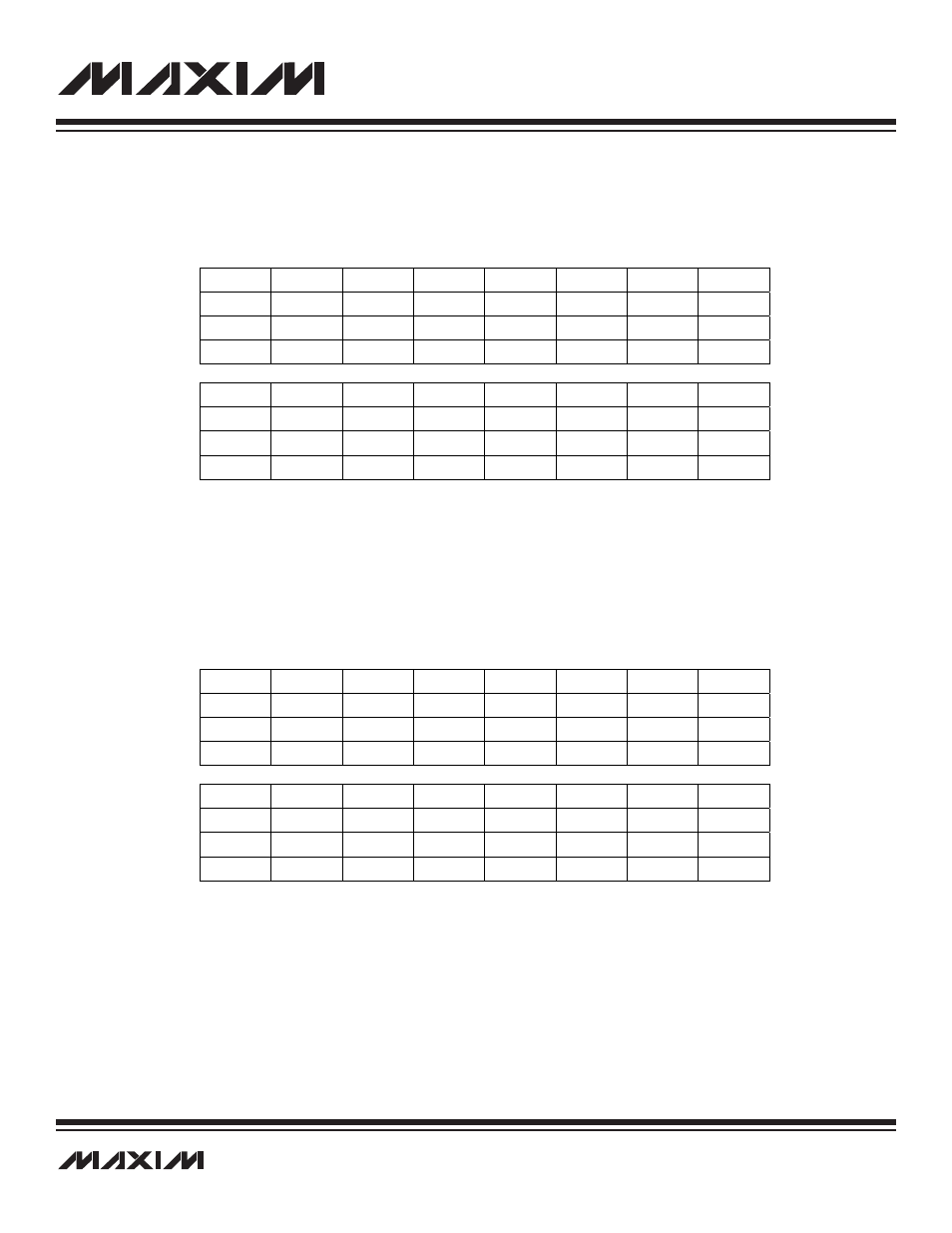

4.1.25 Frame Pointer Register (FP)

Register Description:

Frame Pointer Register

Register Name:

FP

Register Address:

Module 0Eh, Index 0Bh

Bits 15 to 0: Frame Pointer Register Bits 15:0 (FP[15:0]). This register provides the current value of the frame pointer (BP[OFFS]).

4.1.26 Data Pointer 0 Register (DP[0])

Register Description:

Data Pointer 0 Register

Register Name:

DP[0]

Register Address:

Module 0Fh, Index 03h

Bits 15 to 0: Data Pointer 0 Register Bits 15:0 (DP[0][15:0]). This register is used as a pointer to access data memory. DP[0] can

be automatically incremented or decremented following each read operation or can be automatically incremented or decremented

before each write operation.

Bit #

15

14

13

12

11

10

9

8

Name

FP15

FP14

FP13

FP12

FP11

FP10

FP9

FP8

Reset

0

0

0

0

0

0

0

0

Access

r

r

r

r

r

r

r

r

Bit #

7

6

5

4

3

2

1

0

Name

FP7

FP6

FP5

FP4

FP3

FP2

FP1

FP0

Reset

0

0

0

0

0

0

0

0

Access

r

r

r

r

r

r

r

r

r = read

Note: This register is cleared to 0000h on all forms of reset.

Bit #

15

14

13

12

11

10

9

8

Name

DP[0]15

DP[0]14

DP[0]13

DP[0]12

DP[0]11

DP[0]10

DP[0]9

DP[0]8

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

Bit #

7

6

5

4

3

2

1

0

Name

DP[0]7

DP[0]6

DP[0]5

DP[0]4

DP[0]3

DP[0]2

DP[0]1

DP[0]0

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

r = read, w = write

Note: This register is cleared to 0000h on all forms of reset.