4 external interrupt fla, Maxq7667 user’s guide, 4 external interrupt flag register (port 1) (eif1) – Maxim Integrated MAXQ7667 User Manual

Page 82

5-7

___________________________________________________________________________________________________________

MAXQ7667 User’s Guide

5.2.4 External Interrupt Flag Register (Port 1) (EIF1)

Register Description:

External Interrupt Flag Register (Port 1)

Register Name:

EIF1

Register Address:

Module 00h, Index 04h

Bits 15 to 8: Reserved. Read returns 0, write ignored.

Bit 7: Interrupt 7 Edge Detect (IE7). This bit is set when a negative edge (IT7 = 1) or a positive edge (IT7 = 0) is detected on the inter-

rupt 7 pin. Setting this bit to 1 generates an interrupt to the CPU if enabled. This bit remains set until cleared by software or a reset. It

must be cleared by software before exiting the interrupt source routine or another interrupt will be generated as long as this bit is set.

Bit 6: Interrupt 6 Edge Detect (IE6). This bit is set when a negative edge (IT6 = 1) or a positive edge (IT6 = 0) is detected on the inter-

rupt 6 pin. Setting this bit to 1 generates an interrupt to the CPU if enabled. This bit remains set until cleared by software or a reset. It

must be cleared by software before exiting the interrupt source routine or another interrupt will be generated as long as this bit is set.

Bit 5: Interrupt 5 Edge Detect (IE5). This bit is set when a negative edge (IT5 = 1) or a positive edge (IT5 = 0) is detected on the inter-

rupt 5 pin. Setting this bit to 1 generates an interrupt to the CPU if enabled. This bit remains set until cleared by software or a reset. It

must be cleared by software before exiting the interrupt source routine or another interrupt will be generated as long as this bit is set.

Bit 4: Interrupt 4 Edge Detect (IE4). This bit is set when a negative edge (IT4 = 1) or a positive edge (IT4 = 0) is detected on the inter-

rupt 4 pin. Setting this bit to 1 generates an interrupt to the CPU if enabled. This bit remains set until cleared by software or a reset. It

must be cleared by software before exiting the interrupt source routine or another interrupt will be generated as long as this bit is set.

Bit 3: Interrupt 3 Edge Detect (IE3). This bit is set when a negative edge (IT3 = 1) or a positive edge (IT3 = 0) is detected on the inter-

rupt 3 pin. Setting this bit to 1 generates an interrupt to the CPU if enabled. This bit remains set until cleared by software or a reset. It

must be cleared by software before exiting the interrupt source routine or another interrupt will be generated as long as this bit is set.

Bit 2: Interrupt 2 Edge Detect (IE2). This bit is set when a negative edge (IT2 = 1) or a positive edge (IT2 = 0) is detected on the inter-

rupt 2 pin. Setting this bit to 1 generates an interrupt to the CPU if enabled. This bit remains set until cleared by software or a reset. It

must be cleared by software before exiting the interrupt source routine or another interrupt will be generated as long as this bit is set.

Bit 1: Interrupt 1 Edge Detect (IE1). This bit is set when a negative edge (IT1 = 1) or a positive edge (IT1 = 0) is detected on the inter-

rupt 1 pin. Setting this bit to 1 generates an interrupt to the CPU if enabled. This bit remains set until cleared by software or a reset. It

must be cleared by software before exiting the interrupt source routine or another interrupt will be generated as long as this bit is set.

Bit 0: Interrupt 0 Edge Detect (IE0). This bit is set when a negative edge (IT0 = 1) or a positive edge (IT0 = 0) is detected on the inter-

rupt 0 pin. Setting this bit to 1 generates an interrupt to the CPU if enabled. This bit remains set until cleared by software or a reset. It

must be cleared by software before exiting the interrupt source routine or another interrupt will be generated as long as this bit is set.

r = read, w = write

Note: This register is cleared to 00h on all forms of reset.

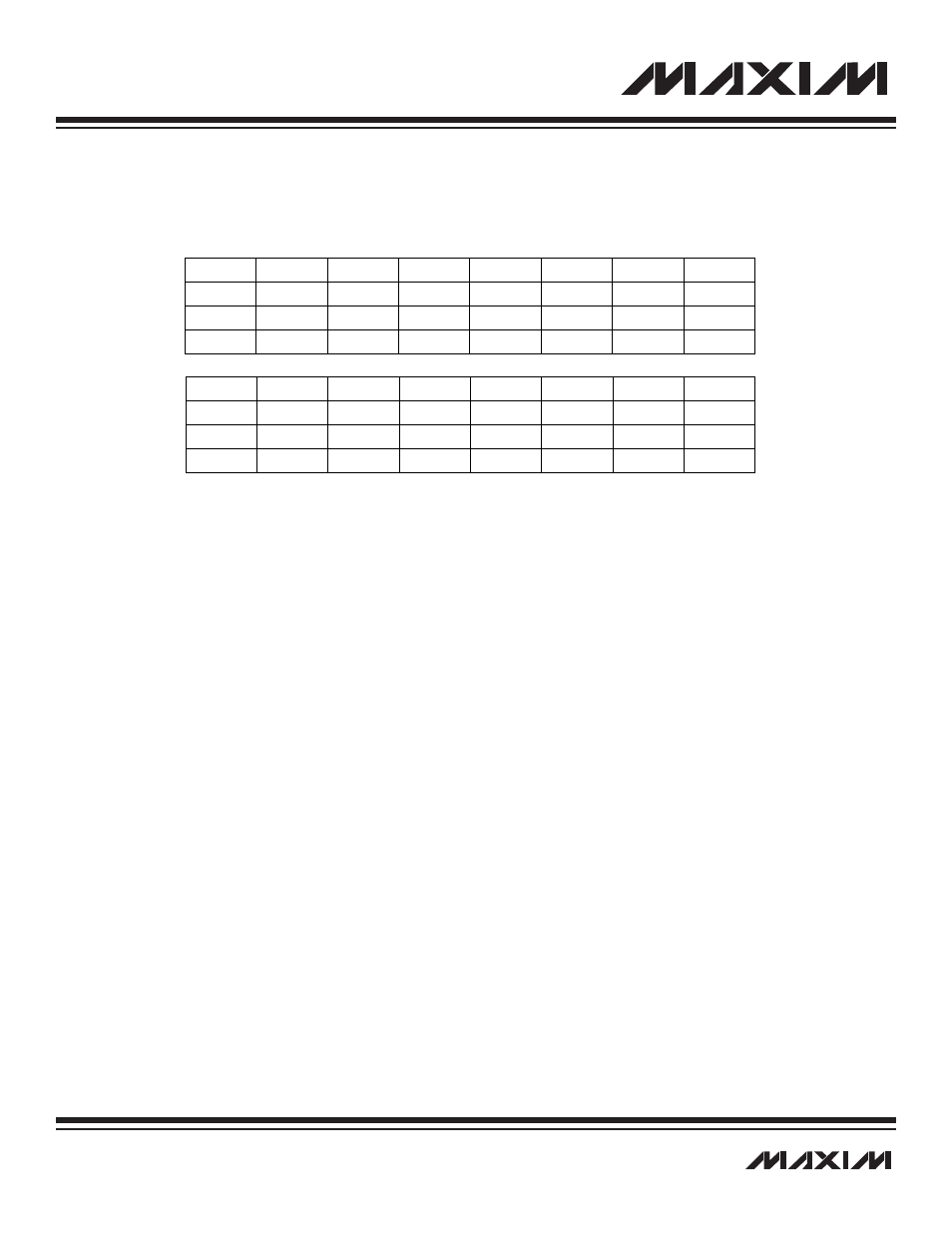

Bit #

15

14

13

12

11

10

9

8

Name

—

—

—

—

—

—

—

—

Reset

0

0

0

0

0

0

0

0

Access

r

r

r

r

r

r

r

r

Bit #

7

6

5

4

3

2

1

0

Name

IE7

IE6

IE5

IE4

IE3

IE2

IE1

IE0

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw