3 echo receive data reg, Table 17-9. echo receive path interrupts -24, 3 echo receive data register -24 – Maxim Integrated MAXQ7667 User Manual

Page 306: Maxq7667 user’s guide, Table 17-9. echo receive path interrupts, 3 echo receive data register

17.5.3 Echo Receive Data Register

The LPFD register contains the most recent filtered and processed data. Reading LPFD does not clear it. The data in LPFD is updat-

ed as soon as a new value is available. The LPFD data is in straight binary format.

When a new LPF value is ready, the data ready flag, LPFRDY (ASR.1), is set to 1. If the echo envelope LPF output data ready interrupt

enable bit, LPFIE (AIE.2), is set to 1, an interrupt is generated by the LPFRDY flag.

The FIFO has a data pointer, FFDP[3:0] (LPFC.11:8), that indicates space taken up in the FIFO. A value of 0 indicates that the FIFO is

empty and a value of 8 indicates that it is full.

The FIFO holds a maximum of eight filter readings and this data can be read from the Echo Envelope Lowpass Filter FIFO Output reg-

ister (LPFF). When LPFF is read, the read data is automatically popped off the stack and the next reading is available.

Note: The data

read from an empty FIFO (FFDP = 0) should be considered invalid. However, due to the FIFO’s implementation, it is most likely to be

a previous sample value and may appear valid. So the depth value (FFDP) should always be tested before reading the FIFO.

Four FIFO interrupt level bits, FFIL[3:0] (LPFC.15:12), in the Echo Envelope Lowpass Filter FIFO Control register (LPFC) can be set to

generate an interrupt whenever FFDP matches FFIL. This interrupt is enabled only when LFLIE (AIE.2) is set to 1. An exception to this

is when FFIL = 0; setting FFIL to 0 disables FFIL interrupts (even with LFLIE = 1).

Another interrupt occurs due to the overflowing of the FIFO. This is indicated by the FIFO overflow flag, FFOV (LPFC.7). This bit is set

whenever the FIFO is already full and an attempt has been made to write to the FIFO. The data that would have been written to the

FIFO is lost, and an interrupt may be generated.

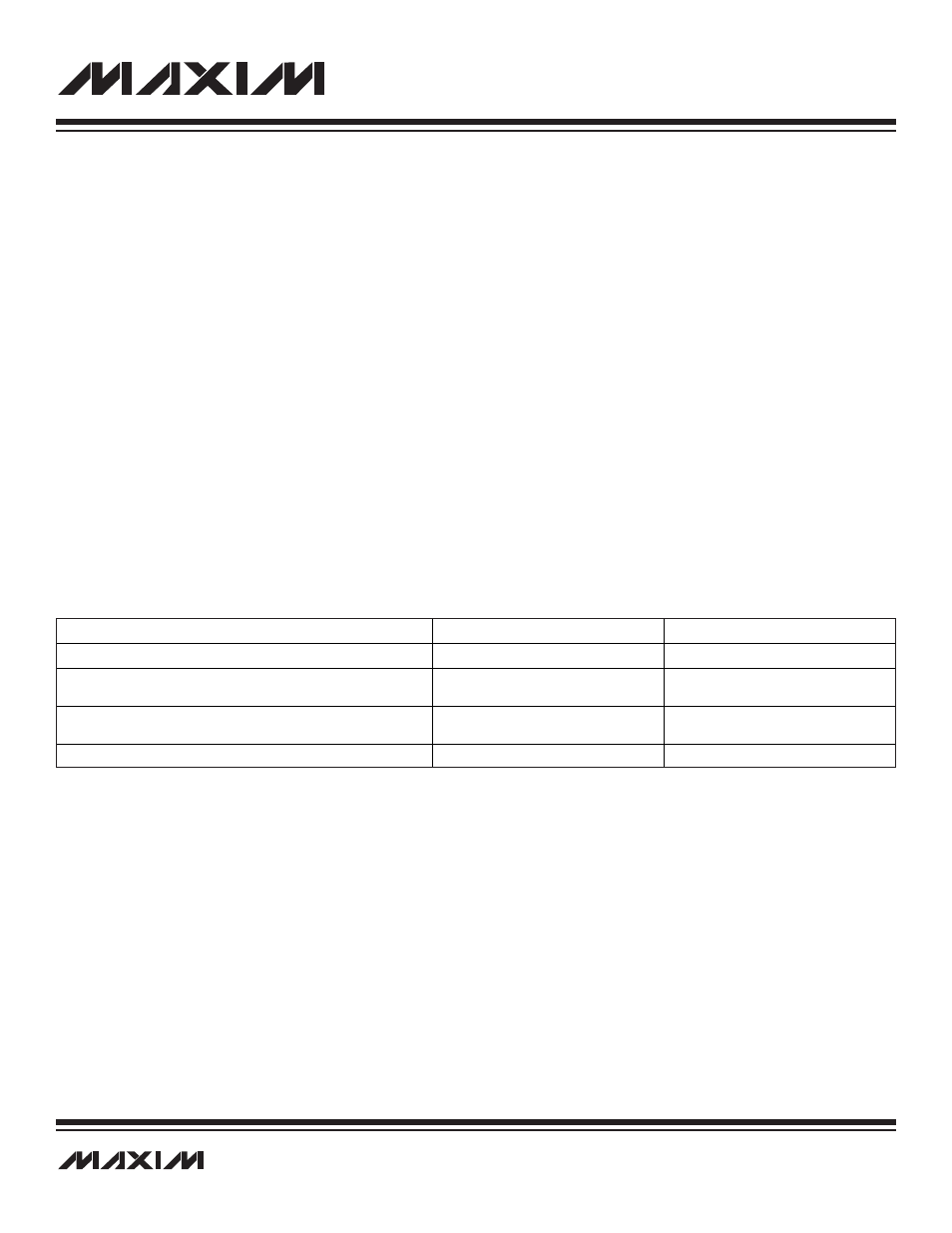

Table 17-9 summarizes the interrupts that can be generated by the echo receive path, the data they are associated with, and how they

are enabled.

All the above-mentioned interrupts are affected by the setting of the MAXQ global interrupt enable (IGE) and the module interrupt

enable for Module 5. To enable interrupts, both the global and module interrupts must be enabled.

Table 17-9. Echo Receive Path Interrupts

_________________________________________________________________________________________________________

17-24

MAXQ7667 User’s Guide

INTERRUPT CONDITION

STATUS BIT SET BY INTERRUPT

INTERRUPT ENABLED BY

LPF data ready.

LPFRDY (ASR.1)

LPFIE = 1 (AIE.1)

LPF FIFO depth is equal to the lowpass interrupt level, FFDP = FFIL.

(No interrupts are generated for FFIL = 0.)

LPFFL (ASR.2)

LFLIE = 1 (AIE.2)

LPF FIFO overflow (an attempt was made to put data in the FIFO, but

it was already full).

FFOV (LPFC.7)

May be enabled

Comparator output is high.

CMPI (ASR.3)

CMPIE (AIE.3)