2 schedule timer register, 1 schedule timer control, 2 schedule timer register descriptions -3 – Maxim Integrated MAXQ7667 User Manual

Page 128: 1 schedule timer control register (scnt) -3, Maxq7667 user’s guide, 2 schedule timer register descriptions, 1 schedule timer control register (scnt)

7-3

___________________________________________________________________________________________________________

MAXQ7667 User’s Guide

7.2 Schedule Timer Register Descriptions

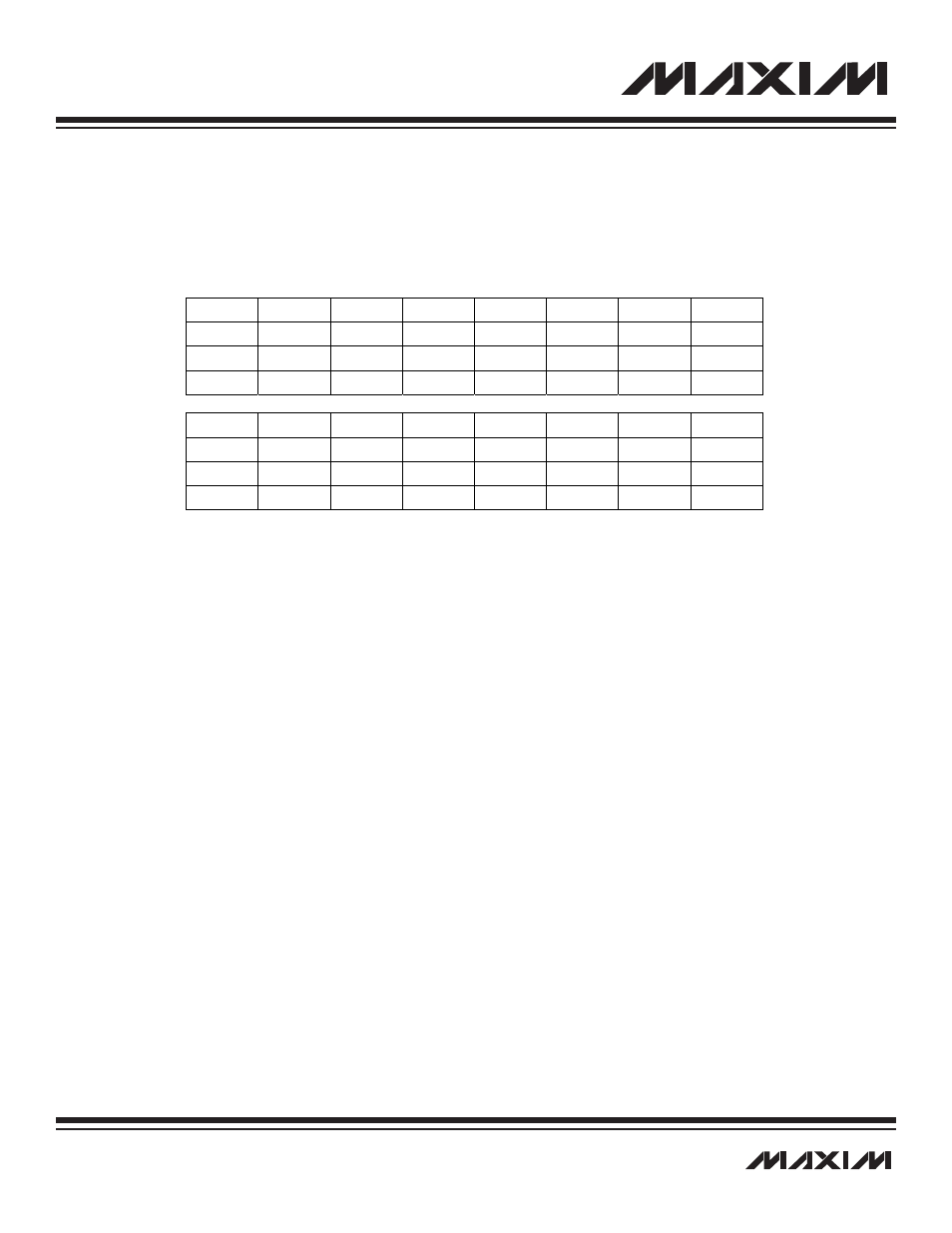

7.2.1 Schedule Timer Control Register (SCNT)

Register Description:

Schedule Timer Control Register

Register Name:

SCNT

Register Address:

Module 01h, Index 0Eh

Bits 15 to 12, 5 to 2: Reserved. Read as 0.

Bits 11 to 9: Schedule Timer Prescaler Division Ratio (STDIV[2:0]). The clock used by the schedule timer is divided down from sys-

tem clock, by the following factors:

0: divided by 1

1: divided by 2

2: divided by 4

3: divided by 8

4: divided by 16

5: divided by 32

6: divided by 64

7: divided by 128

Bit 8: Schedule Synchronization Enable (SSYNC_EN). When set to 1, external synchronization event (from pin SYNC) is enabled. It

is cleared after such event occurs.

Bit 7: Schedule Alarm Interrupt Enable (SALIE). When set to 1 the schedule alarm interrupt gets enabled. Setting this bit to 0 dis-

ables the schedule alarm interrupt. When enabled and SALMF = 1, an interrupt is generated.

Bit 6: Schedule Alarm Flag (SALMF). This bit is set when both STIME and SALME are 1 and STIM equals SALM.

Bit 1: Schedule Timer Alarm Enable (SALME). When set to 1 the schedule alarm function is enabled. Setting this bit to 0 disables

the schedule alarm function.

Bit 0: Schedule Timer Enable (STIME). When set to 1 the schedule timer is enabled. Setting this bit to 0 disables the schedule timer.

Bit #

15

14

13

12

11

10

9

8

Name

—

—

—

—

STDIV2

STDIV1

STDIV0

SSYNC_EN

Reset

0

0

0

0

0

0

0

0

Access

r

r

r

r

rw

rw

rw

rw

Bit #

7

6

5

4

3

2

1

0

Name

SALIE

SALMF

—

—

—

—

SALME

STIME

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

r

r

r

r

rw

rw

r = read, w = write

Note: This register is cleared to 000h on all forms of reset.