3 serial port buffer reg, 4 fifo status register, 3 serial port buffer register (sbuf) -7 – Maxim Integrated MAXQ7667 User Manual

Page 137: 4 fifo status register (uart) (fstat) -7, Maxq7667 user’s guide, 3 serial port buffer register (sbuf), 4 fifo status register (uart) (fstat)

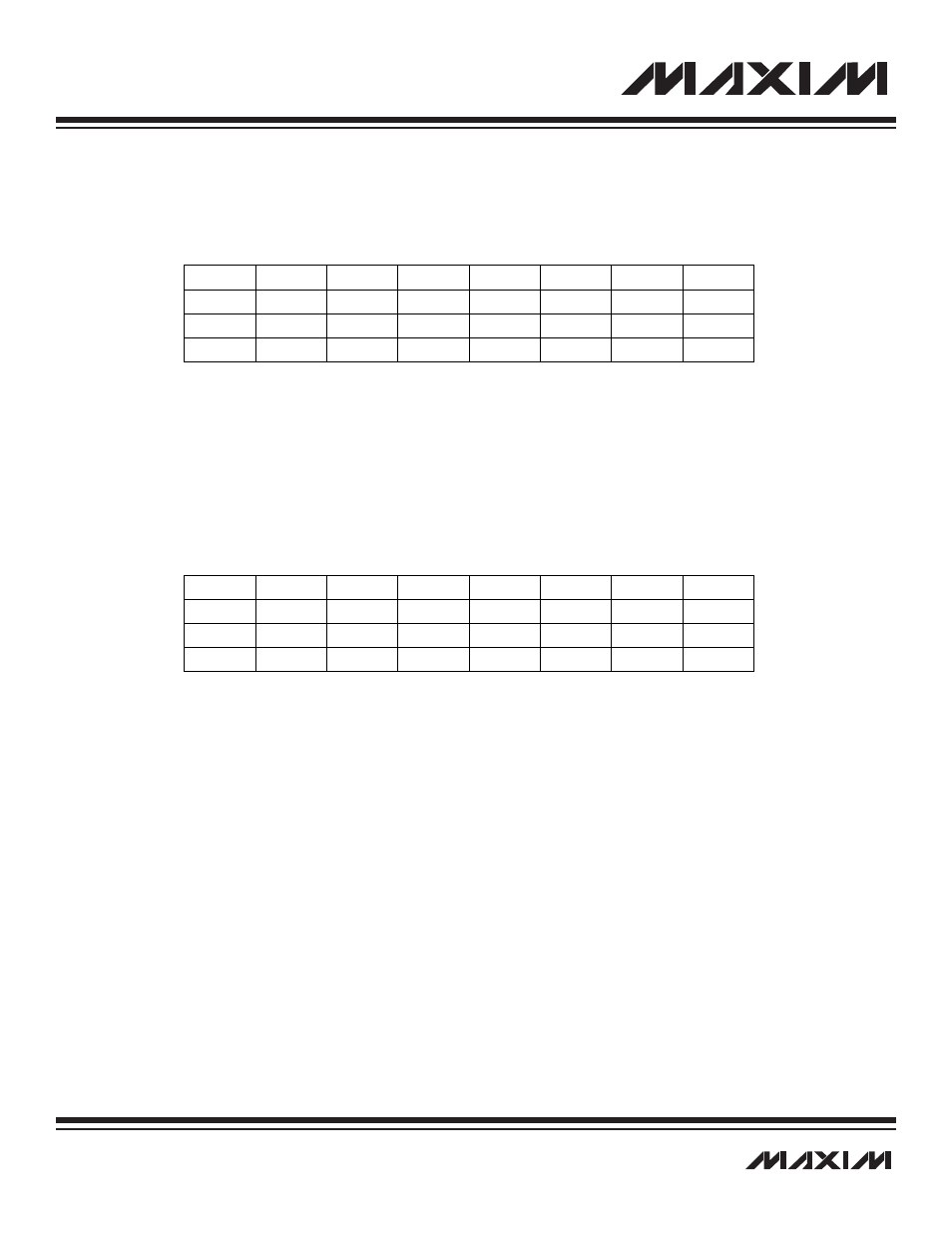

8.3.3 Serial Port Buffer Register (SBUF)

Register Description:

Serial Port Buffer Register

Register Name:

SBUF

Register Address:

Module 03h, Index 07h

Bits 7 to 0: Serial Port Buffer Register (SBUF[7:0]). This register is the access point for inserting data into the transmit buffer or

retrieving data from the receive buffer. To load the transmit FIFO, software will normally write to this register once for each byte of data

to be transmitted. Similarly, when a frame has been received, software will normally read this register until the receive FIFO is empty.

8.3.4 FIFO Status Register (UART) (FSTAT)

Register Description:

FIFO Status Register

Register Name:

FSTAT

Register Address:

Module 03h, Index 0Ch

Bits 7 and 6: Reserved. Read returns 0.

Bit 5: Transmit FIFO Full (TFF). This bit is set to 1 by the peripheral when the transmit FIFO is completely full. The bit is automatical-

ly cleared to 0 when a byte of data has been transmitted.

Bit 4: Transmit FIFO Almost Empty (TFAE). This bit is set to 1 by the peripheral when the amount of data in the transmit FIFO exceeds

the threshold configured by the TXFT[1:0] field (FCON.5:4).

Bit 3: Transmit FIFO Empty (TFE). This bit is set to 1 by the peripheral whenever the transmit FIFO is completely empty.

Bit 2: Receive FIFO Full (RFF). This bit is set to 1 by the peripheral whenever the receive FIFO is completely full.

Bit 1: Receive FIFO Almost Full (RFAF). This bit is set to 1 by the peripheral when the amount of data in the receive FIFO exceeds

the threshold configured by the RXFT[1:0] field (FCON.3:2).

Bit 0: Receive FIFO Empty (RFE). This bit is set to 1 by the peripheral whenever the receive FIFO is completely empty.

8-7

___________________________________________________________________________________________________________

MAXQ7667 User’s Guide

r = read, w = write

Note: SBUF is cleared to 00h on all forms of reset.

Bit #

7

6

5

4

3

2

1

0

Name

SBUF7

SBUF6

SBUF5

SBUF4

SBUF3

SBUF2

SBUF1

SBUF0

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

r = read

Note: FSTAT is cleared to 09h on all forms of reset.

Bit #

7

6

5

4

3

2

1

0

Name

—

—

TFF

TFAE

TFE

RFF

RFAF

RFE

Reset

0

0

0

0

1

0

0

1

Access

r

r

r

r

r

r

r

r