9 effective address calculation – Renesas H8S/2111B User Manual

Page 78

Rev. 1.00, 05/04, page 44 of 544

2.7.9 Effective

Address

Calculation

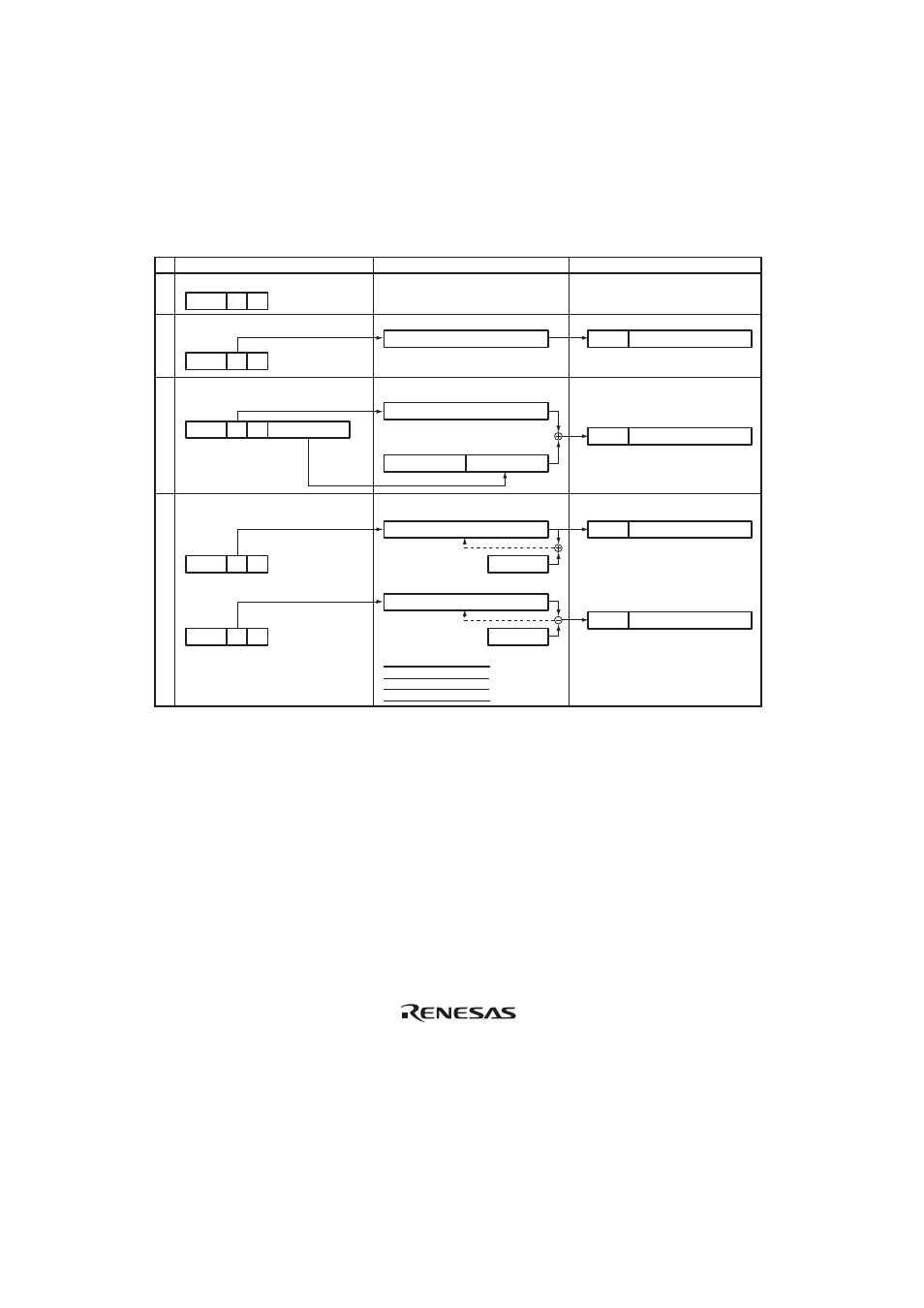

Table 2.13 indicates how effective addresses are calculated in each addressing mode. In normal

mode, the upper 8 bits of the effective address are ignored in order to generate a 16-bit address.

Table 2.13 Effective Address Calculation (1)

No

1

Offset

1

2

4

r

op

31

0

31

23

2

3

Register indirect with displacement

@(d:16,ERn) or @(d:32,ERn)

4

r

op

disp

r

op

rm

op

rn

31

0

31

0

r

op

Don't care

31

23

31

0

Don't care

31

0

disp

31

0

31

0

31

23

31

0

Don't care

31

23

31

0

Don't care

24

24

24

24

Addressing Mode and Instruction Format

Effective Address Calculation

Effective Address (EA)

Register direct (Rn)

General register contents

General register contents

General register contents

General register contents

Sign extension

Register indirect (@ERn)

Register indirect with post-increment or

pre-decrement

• Register indirect with post-increment @ERn+

• Register indirect with pre-decrement @-ERn

1, 2, or 4

1, 2, or 4

Operand Size

Byte

Word

Longword

Operand is general register contents.