2 output compare output timing, 3 frc clear timing – Renesas H8S/2111B User Manual

Page 205

Rev. 1.00, 05/04, page 171 of 544

9.5.2

Output Compare Output Timing

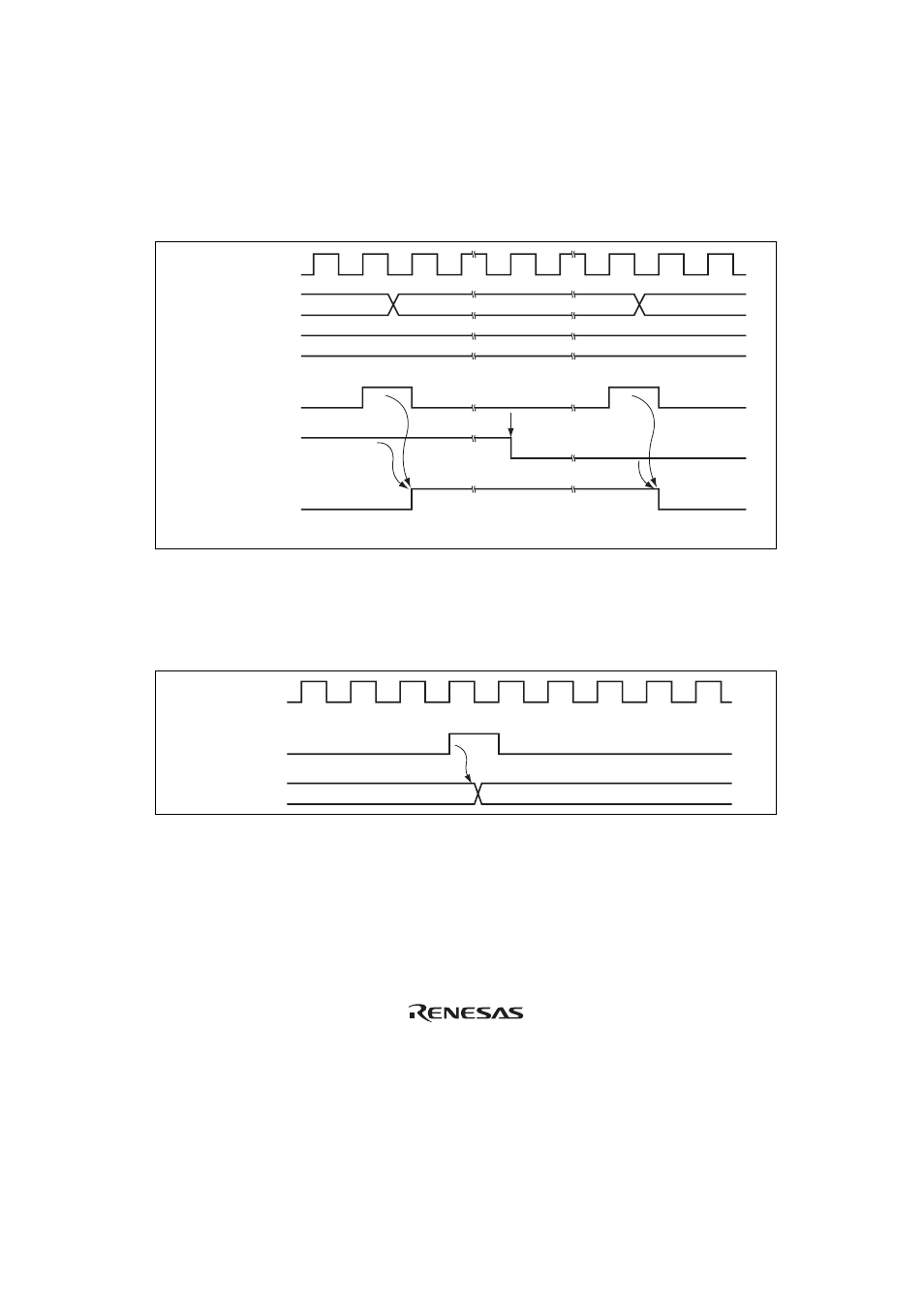

A compare-match signal occurs at the last state when the FRC and OCR values match (at the

timing when the FRC updates the counter value). When a compare-match signal occurs, the level

selected by the OLVL bit in TOCR is output at the output compare pin (FTOA or FTOB). Figure

9.5 shows the timing of this operation for compare-match A.

φ

FRC

OCRA

N

N

N + 1

N + 1

N

N

Compare-match

A signal

OLVLA

Output compare A

output pin FTOA

Clear*

Note: * Indicates instruction execution by software.

Figure 9.5 Timing of Output Compare A Output

9.5.3 FRC

Clear

Timing

FRC can be cleared when compare-match A occurs. Figure 9.6 shows the timing of this operation.

φ

FRC

N

H'0000

Compare-match

A signal

Figure 9.6 Clearing of FRC by Compare-Match A Signal