Renesas H8S/2111B User Manual

Page 364

Rev. 1.00, 05/04, page 330 of 544

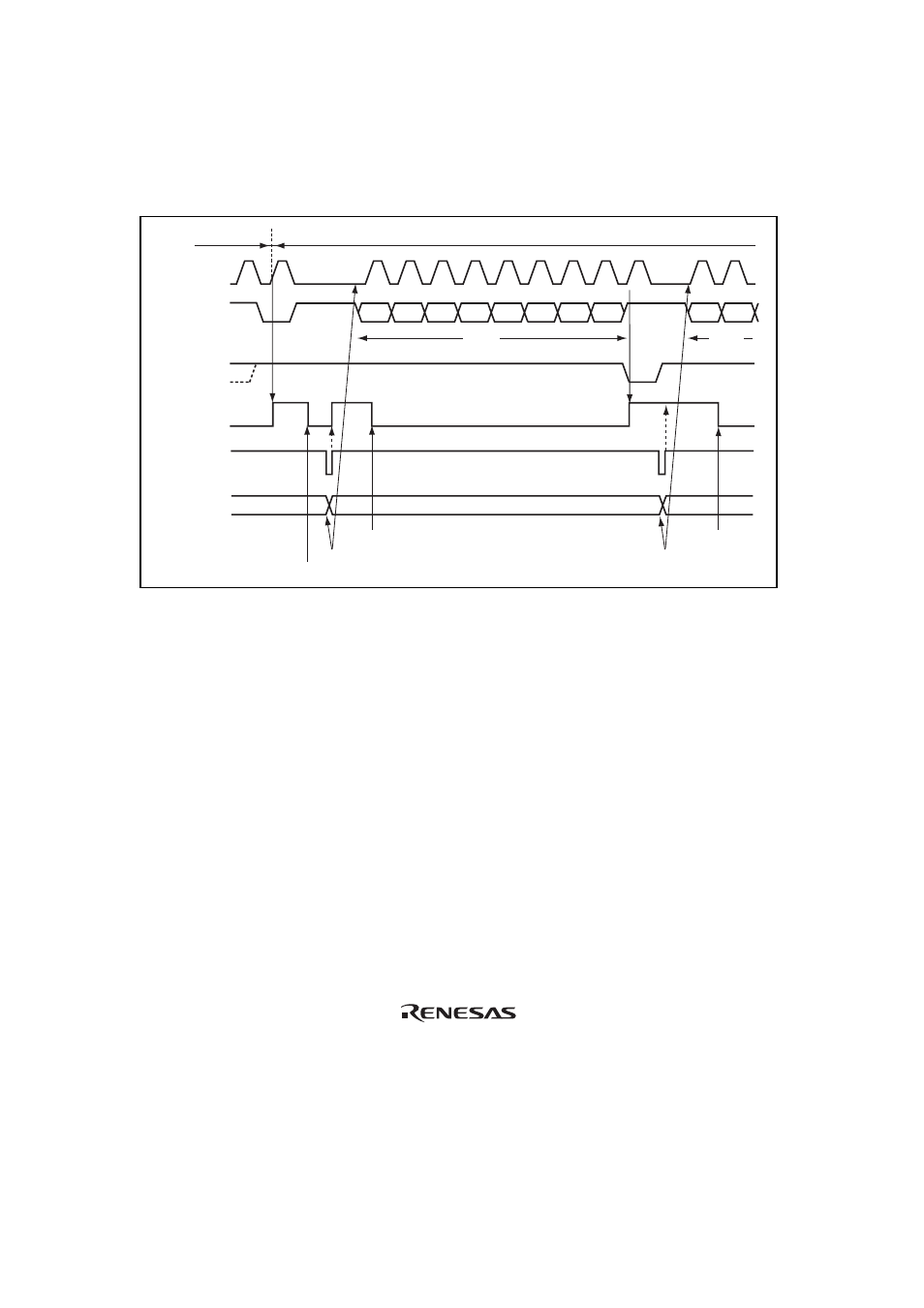

10. When the stop condition is detected, that is, when SDA is changed from low to high when SCL

is high, the BBSY flag in ICCR is cleared to 0 and the STOP flag in ICSR is set to 1. When the

STOPIM bit in ICXR is 0, the IRIC flag is set to 1. If the IRIC flag has been set, it is cleared

to 0.

SDA

(master output)

SDA

(slave output)

2

1

2

1

4

3

6

5

8

7

9

9

8

Bit 7

Bit 6

Bit 5

Bit 7

Bit 6

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

ICDRE

ICDR

IRIC

SCL

(master output)

Slave receive mode

Slave transmit mode

[3] ICDR write

User processing

Data 1

Data 1

Data 2

Data 2

A

R/

W

A

[4]

[3] IRIC clear

[3] IRIC clear

[5] IRIC clear

[5] ICDR write

[2]

Figure 13.24 Example of Slave Transmit Mode Operation Timing

(MLS = 0)

This manual is related to the following products: