6 interrupt sources, 7 usage notes, 1 conflict between frc write and clear – Renesas H8S/2111B User Manual

Page 211

Rev. 1.00, 05/04, page 177 of 544

9.6 Interrupt

Sources

The free-running timer can request seven interrupts: ICIA to ICID, OCIA, OCIB, and FOVI. Each

interrupt can be enabled or disabled by an enable bit in TIER. Independent signals are sent to the

interrupt controller for each interrupt. Table 9.2 lists the sources and priorities of these interrupts.

Table 9.2

FRT Interrupt Sources

Interrupt Interrupt

Source

Interrupt Flag

Priority

ICIA

Input capture of ICRA

ICFA

High

ICIB

Input capture of ICRB

ICFB

ICIC

Input capture of ICRC

ICFC

ICID

Input capture of ICRD

ICFD

OCIA

Compare match of OCRA

OCFA

OCIB

Compare match of OCRB

OCFB

FOVI

Overflow of FRC

OVF

Low

9.7 Usage

Notes

9.7.1

Conflict between FRC Write and Clear

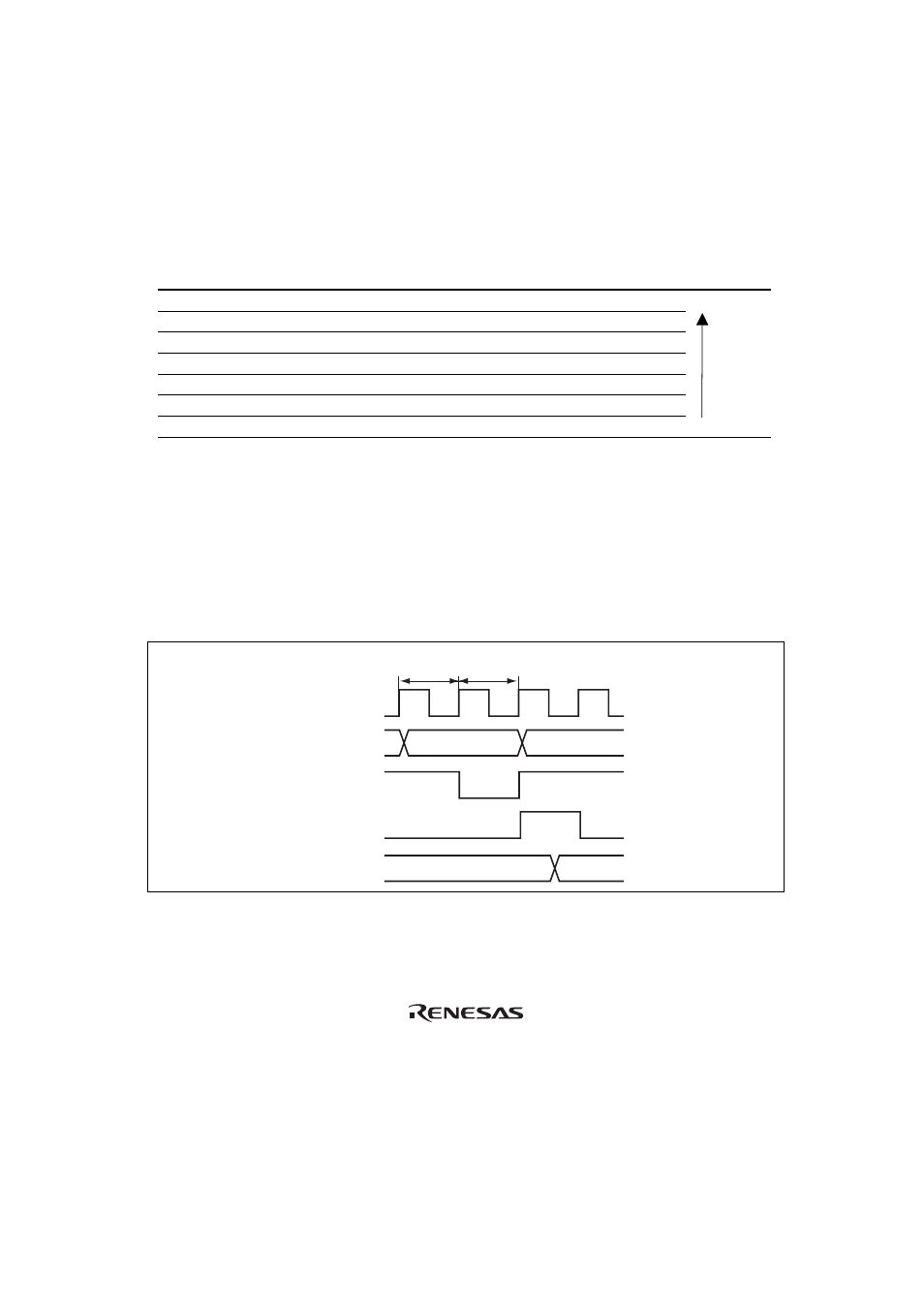

If an internal counter clear signal is generated during the state after an FRC write cycle, the clear

signal takes priority and the write is not performed. Figure 9.17 shows the timing for this type of

conflict.

φ

Address

FRC address

Internal write

signal

Counter clear

signal

FRC

N

H'0000

T

1

T

2

Write cycle of FRC

Figure 9.17 FRC Write-Clear Conflict