3 reso signal output timing, 5 interrupt sources – Renesas H8S/2111B User Manual

Page 264

Rev. 1.00, 05/04, page 230 of 544

11.4.3

RESO Signal Output Timing

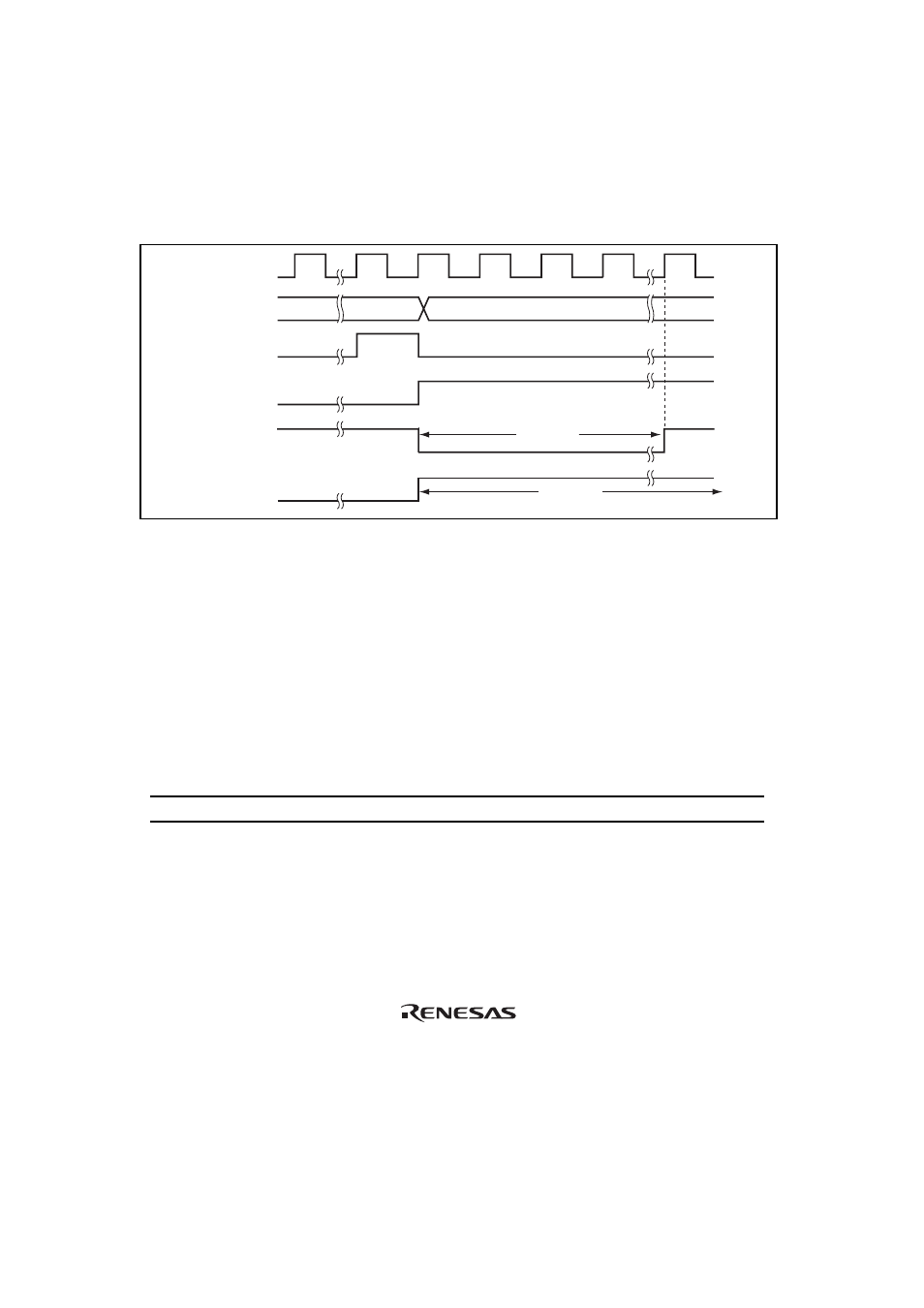

When TCNT overflows in watchdog timer mode, the OVF bit in TCSR is set to 1. When the

RST/

NMI bit is 1 here, the internal reset signal is generated for the entire LSI. At the same time,

the low level signal is output from the

RESO pin. The timing is shown in figure 11.5.

φ

TCNT

H'FF

H'00

132 states

518 states

Overflow signal

(internal signal)

OVF

RESO signal

Internal reset

signal

Figure 11.5 Output Timing of

RESO signal

11.5 Interrupt

Sources

During interval timer mode operation, an overflow generates an interval timer interrupt (WOVI).

The interval timer interrupt is requested whenever the OVF flag is set to 1 in TCSR. OVF must be

cleared to 0 in the interrupt handling routine.

When the NMI interrupt request is selected in watchdog timer mode, an NMI interrupt request is

generated by an overflow.

Table 11.2 WDT Interrupt Source

Name

Interrupt Source

Interrupt Flag

WOVI

TCNT overflow OVF