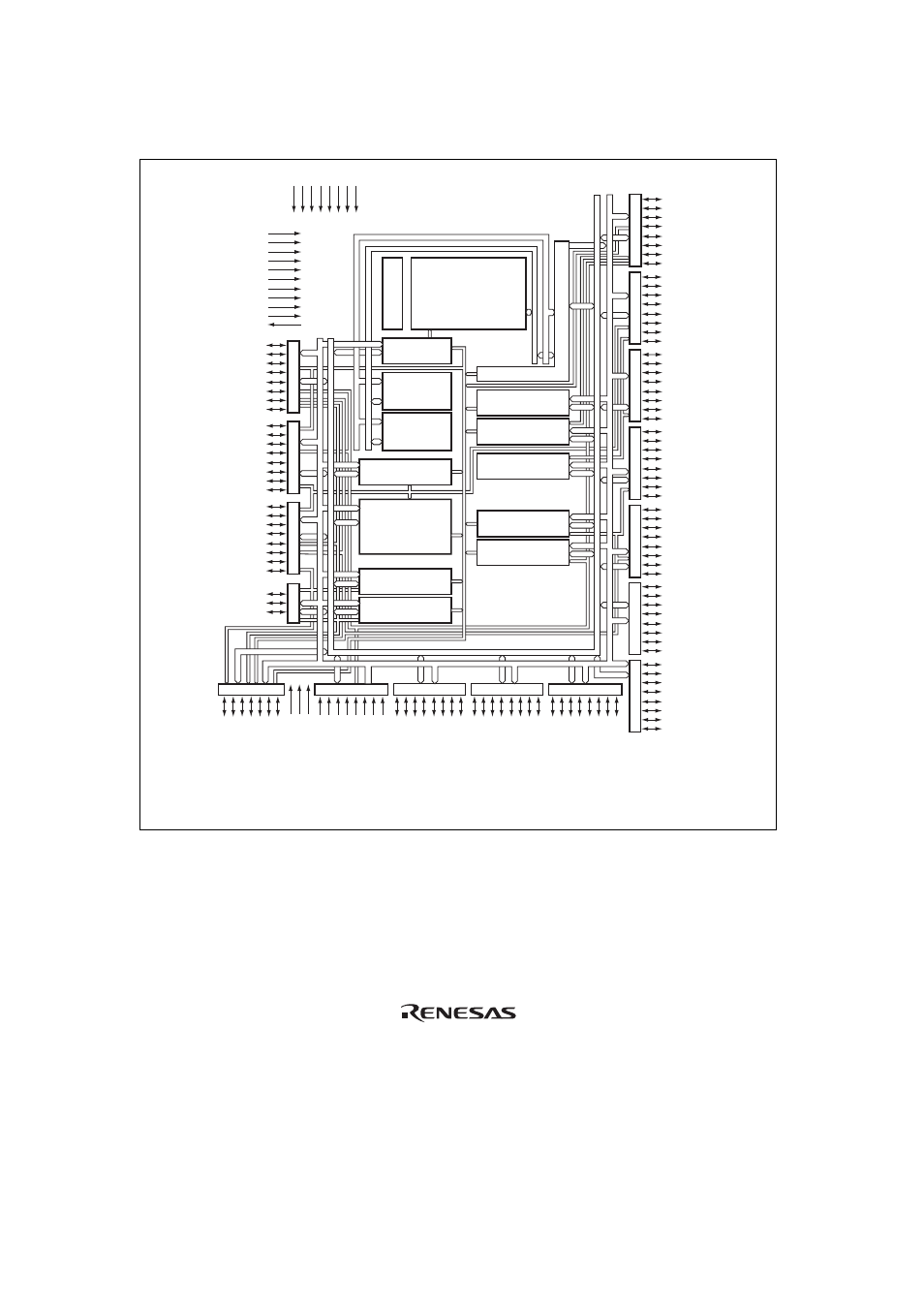

2 internal block diagram, Figure 1.1 internal block diagram – Renesas H8S/2111B User Manual

Page 36

Rev. 1.00, 05/04, page 2 of 544

1.2

Internal Block Diagram

P17/PW7

P16/PW6

P15/PW5

P14/PW4

P13/PW3

P12/PW2

P11/PW1

P10/PW0

P27

P26

P25

P24

P23

P22

P21

P20

PA7/

KIN15/PS2CD

PA6/

KIN14/PS2CC

PA5/

KIN13/PS2BD

PA4/

KIN12/PS2BC

PA3/

KIN11/PS2AD

PA2/

KIN10/PS2AC

PA1/

KIN9

PA0/

KIN8

P37/SERIRQ

P36/LCLK

P35/

LRESET

P34/

LFRAME

P33/LAD3

P32/LAD2

P31/LAD1

P30/LAD0

PB7/

WUE7

PB6/

WUE6

PB5/

WUE5

PB4/

WUE4

PB3/

WUE3

PB2/

WUE2

PB1/

WUE1/LSCI

PB0/

WUE0/LSMI

P97/SDA0

P96/

φ/EXCL

P95

P94

P93

P92/

IRQ0

P91/

IRQ1

P90/

IRQ2/ADTRG

P67/TMOX/

KIN7/IRQ7

P66/FTOB/

KIN6/IRQ6

P65/FTID/

KIN5

P64/FTIC/

KIN4

P63/FTIB/

KIN3

P62/FTIA/

KIN2/TMIY

P61/FTOA/

KIN1

P60/FTCI/

KIN0/TMIX

P47

P46

P45/TMRI1

P44/TMO1

P43/TMCI1

P42/TMRI0/SDA1

P41/TMO0

P40/TMCI0

P52/ExSCK1*/SCL0

P51/ExRxD1*

P50/ExTxD1*

X1

X2

RES

XTAL

EXTAL

VCCB

MD1

MD0

NMI

STBY

RESO

VCC

VCC

VCL

VSS

VSS

VSS

VSS

VSS

PC7

PC6

PC5

PC4

PC3

PC2

PC1

PC0

PD7

PD6

PD5

PD4

PD3

PD2

PD1

PD0

P77

P76

P75/AN5

P74/AN4

P73/AN3

P72/AN2

P71/AN1

P70/AN0

P86/

IRQ5

/SCK1/SCL1

P85/

IRQ4

/RxD1

P84/

IRQ3

/TxD1

P83/

LPCPD

P82/

CLKRUN

P81/GA20

P80/

PME

AVref

AVCC

AVSS

PG7/ExSCLB

*

PG6/ExSDAB

*

PG5/ExSCLA

*

PG4/ExSDAA

*

PG3

PG2

PG1

PG0

PF7/TMOY

*

PF6/ExTMOX

*

PF5/ExTMIY

*

PF4/ExTMIX

*

PF3/TMOB

PF2/TMOA

PF1/TMIB

PF0/TMIA

PE7

PE6

PE5

PE4

PE3

PE2

PE1

PE0

H8S/2000 CPU

Interrup

controller

WDT

× 2 channels

ROM

(Flash memory)

RAM

8-bit PWM

16-bit FRT

8-bit timer

× 6 channels

Host interfaces

(LPC)

10-bit A/D converter

SCI

× 1 channel

IIC

× 2 channels

Port 8

Port 7

Port G

Port F

Port E

Clock pulse

generator

Internal data bus

Internal address bus

Bus controller

Port A

Port 2

Port 1

Port 3

Port B

Port C

Port D

Port 9

Port 6

Port 4

Port 5

Note: * The program development tool (emulator) does not support this function.

Keyboard buffer

controller

× 3 channels

Figure 1.1 Internal Block Diagram