Renesas H8S/2111B User Manual

Page 378

Rev. 1.00, 05/04, page 344 of 544

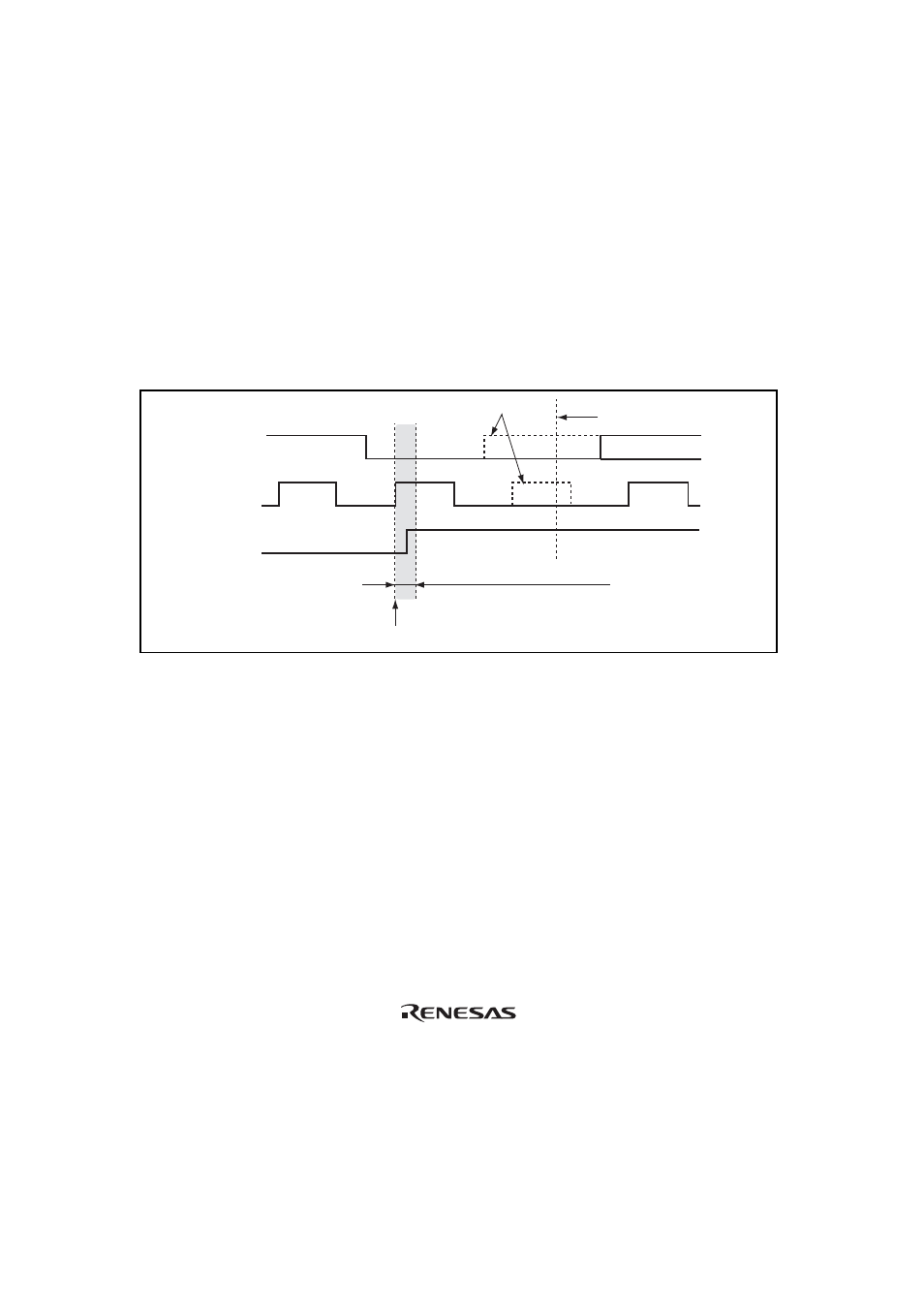

11. Note on ICDR read and ICCR access in slave transmit mode

In I

2

C bus interface slave transmit mode, do not read ICDR or do not read/write from/to ICCR

during the time shaded in figure 13.33. However, such read and write operations cause no

problem in interrupt handling processing that is generated in synchronization with the rising

edge of the 9th clock pulse because the shaded time has passed before making the transition to

interrupt handling.

To handle interrupts securely, be sure to keep either of the following conditions.

Read ICDR data that has been received so far or read/write from/to ICCR before starting

the receive operation of the next slave address.

Monitor the BC2 to BC0 bit counter in ICMR; when the count is 000 (8th or 9th clock

pulse), wait for at least two transfer clock times in order to read ICDR or read/write from/to

ICCR during the time other than the shaded time.

Data transmission

Bit 7

Address reception

SCL

TRS bit

Waveform at problem occurrence

ICDR read and ICCR read/write are disabled

(6 system clock period)

8

R/W

A

9

The rise of the 9th clock is detected

SDA

ICDR write

Figure 13.33 ICDR Read and ICCR Access Timing in Slave Transmit Mode

Note: This restriction on usage can be canceled by setting the FNC1 and FNC0 bits to 1 in

ICXR.