Renesas H8S/2111B User Manual

Page 285

Rev. 1.00, 05/04, page 251 of 544

12.4.2

Receive Data Sampling Timing and Reception Margin in Asynchronous Mode

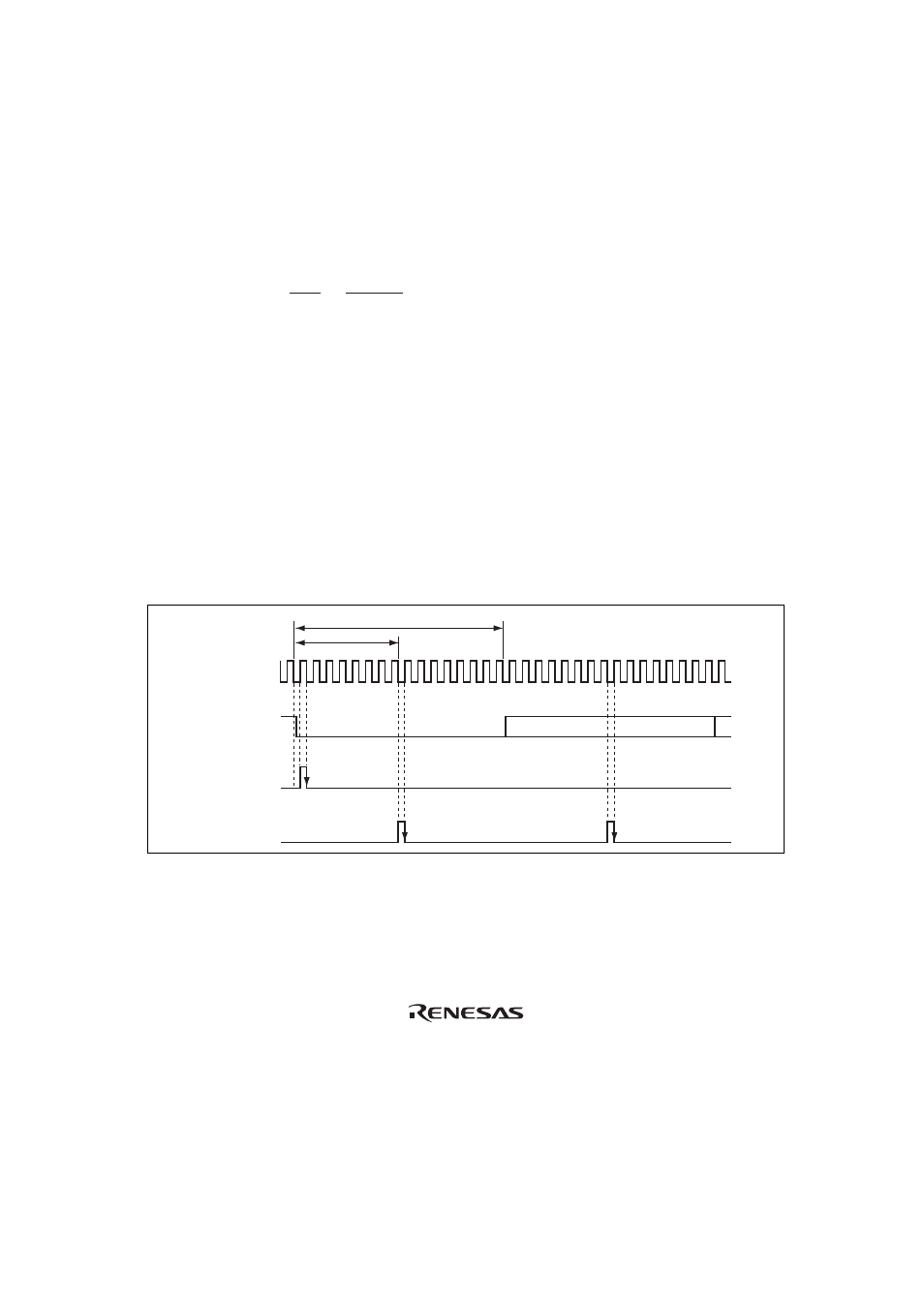

In asynchronous mode, the SCI operates on a basic clock with a frequency of 16 times the bit rate.

In reception, the SCI samples the falling edge of the start bit using the basic clock, and performs

internal synchronization. Since receive data is latched internally at the rising edge of the 8th pulse

of the basic clock, data is latched at the middle of each bit, as shown in figure 12.3. Thus the

reception margin in asynchronous mode is determined by formula (1) below.

M = (0.5 – ) – (1 + F) – (L – 0.5) F } × 100 [%] ... Formula (1)

2N

1

N

D – 0.5

[Legend]

M: Reception margin (%)

N : Ratio of bit rate to clock (N = 16)

D : Clock duty (D = 0.5 to 1.0)

L : Frame length (L = 9 to 12)

F : Absolute value of clock rate deviation

}

Assuming values of F = 0 and D = 0.5 in formula (1), the reception margin is determined by the

formula below.

M = {0.5 – 1/(2 Ч 16)} Ч 100 [%] = 46.875 %

However, this is only the computed value, and a margin of 20% to 30% should be allowed in

system design.

Internal

basic clock

16 clocks

8 clocks

Receive data

(RxD)

Synchronization

sampling timing

Start bit

D0

D1

Data sampling

timing

15 0

7

15 0

0

7

Figure 12.3 Receive Data Sampling Timing in Asynchronous Mode