Figure 9.1 shows a block diagram of the frt – Renesas H8S/2111B User Manual

Page 192

Rev. 1.00, 05/04, page 158 of 544

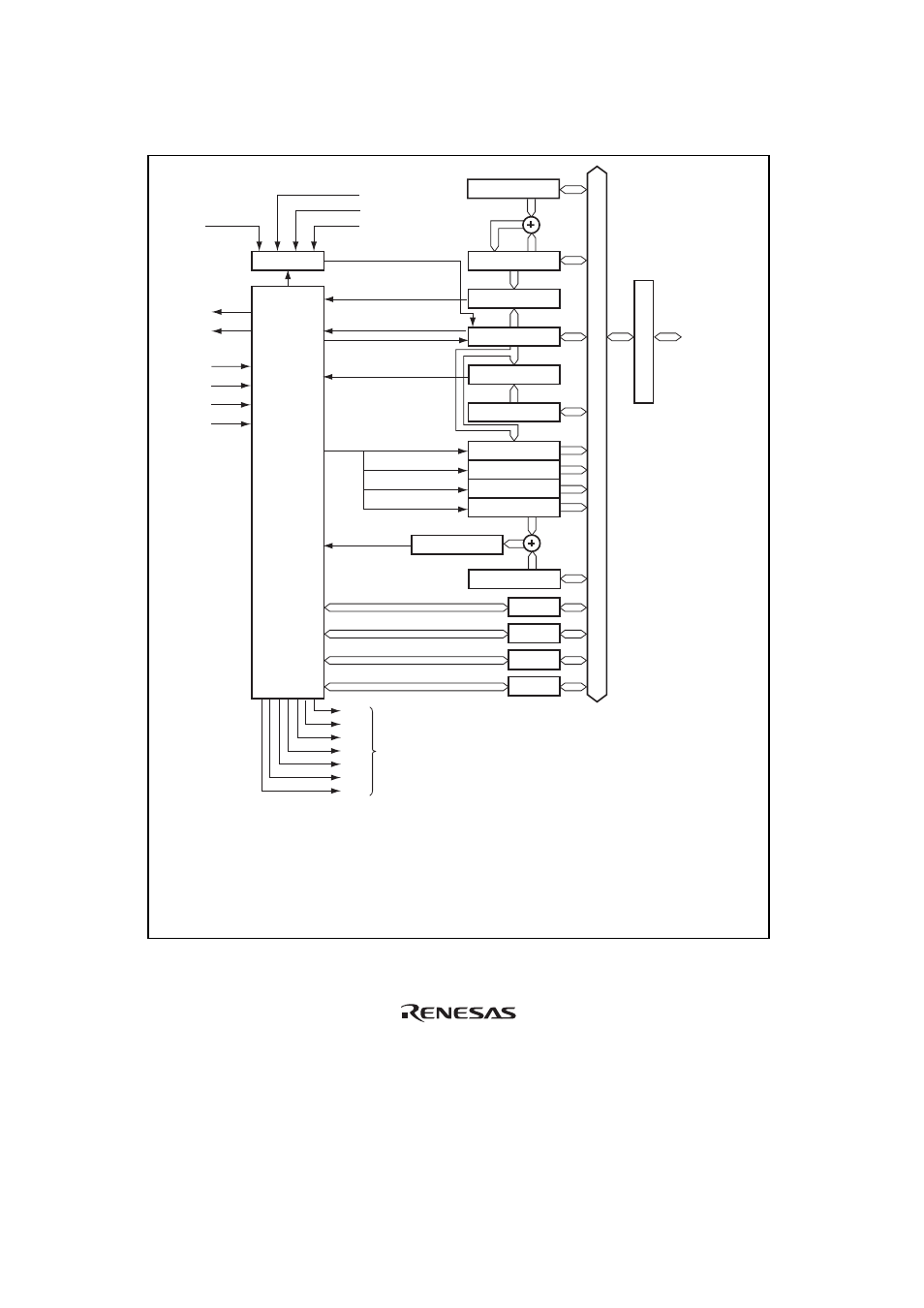

Figure 9.1 shows a block diagram of the FRT.

Clock selector

Clock

Compare-match A

OCRA

Comparator A

Internal data bus

FRC

Comparator B

OCRB

ICRA

ICRB

ICRC

ICRD

TCSR

FTCI

FTOB

FTIA

External clock

Internal clock

φ/2

φ/8

φ/32

FTIB

FTIC

FTID

FTOA

Compare-match B

Overflow

Clear

Input capture

TIER

TCR

TOCR

ICIA

ICIB

ICIC

ICID

Interrupt signal

[Legend]

OCRA, OCRB

OCRAR,OCRAF

OCRDM

FRC

ICRA to ICRD

TCSR

TIER

TCR

TOCR

: Output compare register A, B (16-bit)

: Output compare register AR, AF (16-bit)

: Output compare register DM (16-bit)

: Free-running counter (16-bit)

: Input capture registers A to D (16-bit)

: Timer control/status register (8-bit)

: Timer interrupt enable register (8-bit)

: Timer control register (8-bit)

: Timer output compare control register (8-bit)

OCIA

OCIB

FOVI

OCRAR/F

OCRDM

Comparator M

Compare-match M

Ч 1

Ч 2

Control logic

Module data bus

Bus interface

Figure 9.1 Block Diagram of 16-Bit Free-Running Timer