7 iric setting timing and scl control – Renesas H8S/2111B User Manual

Page 365

Rev. 1.00, 05/04, page 331 of 544

13.4.7 IRIC

Setting

Timing and SCL Control

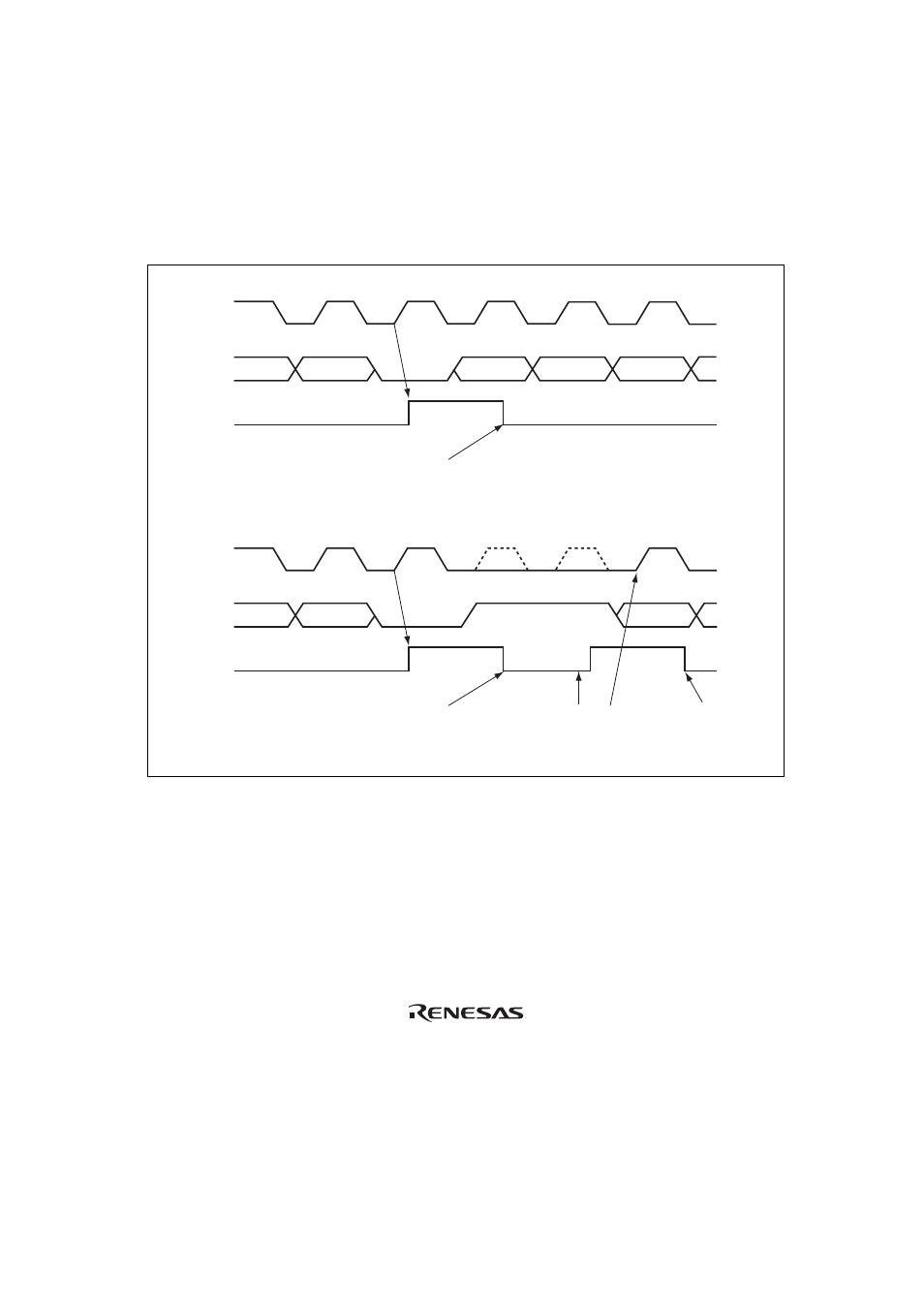

The interrupt request flag (IRIC) is set at different times depending on the WAIT bit in ICMR, the

FS bit in SAR, and the FSX bit in SARX. If the ICDRE or ICDRF flag is set to 1, SCL is

automatically held low after one frame has been transferred in synchronization with the internal

clock. Figures 13.25 to 13.27 show the IRIC set timing and SCL control.

SCL

SDA

IRIC

User processing

Clear IRIC

2

3

1

A

8

7

3

2

1

9

8

7

When WAIT = 0, and FS = 0 or FSX = 0 (I

2

C bus format, no wait)

(a) Data transfer ends with ICDRE = 0 at transmission, or ICDRF = 0 at reception.

(b) Data transfer ends with ICDRE = 1 at transmission, or ICDRF = 1 at reception.

SCL

SDA

IRIC

User processing

Clear IRIC

Clear IRIC

Write to ICDR (transmit)

or read from ICDR (receive)

1

A

8

7

1

9

8

7

Figure 13.25 IRIC Setting Timing and SCL Control (1)