Renesas H8S/2111B User Manual

Page 439

Rev. 1.00, 05/04, page 405 of 544

15.4.5

Host Interface Serialized Interrupt Operation (SERIRQ)

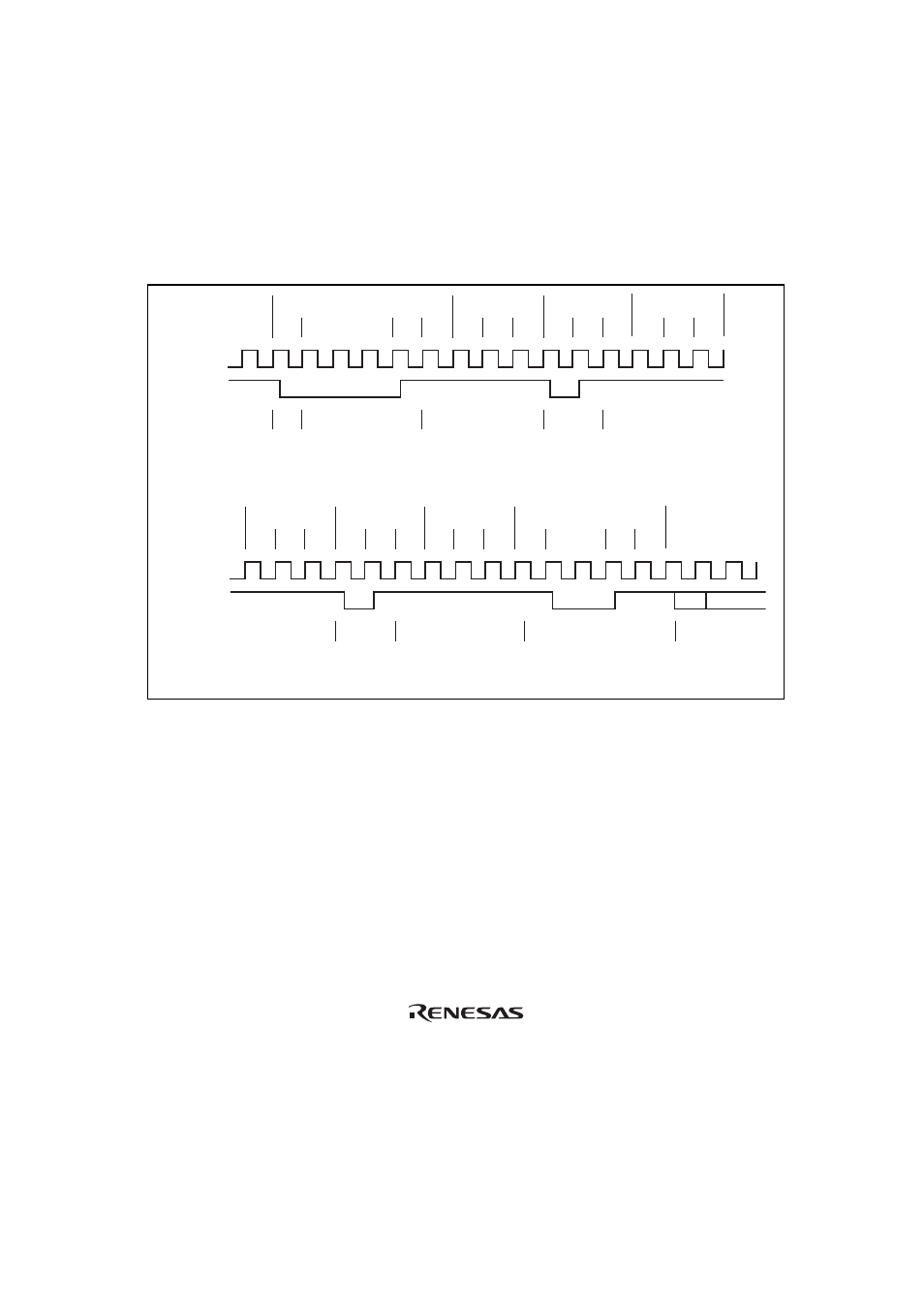

A host interrupt request can be issued from the host interface by means of the SERIRQ pin. In a

host interrupt request via the SERIRQ pin, LCLK cycles are counted from the start frame of the

serialized interrupt transfer cycle generated by the host or a peripheral function, and a request

signal is generated by the frame corresponding to that interrupt. The timing is shown in figure

15.6.

IRQ1

IRQ1

Host controller

None

None

SERIRQ

Drive source

LCLK

START

Start frame

IRQ0 frame

IRQ1 frame

IRQ2 frame

SL

or

H

H

R

T

R

S

T

R

S

T

R

S

T

IRQ15

Host controller

None

None

SERIRQ

Driver

LCLK

START

STOP

IOCHCK frame

Stop frame

Next cycle

IRQ14 frame

IRQ15 frame

R

S

T

R

S

T

R

S

T

R

T

H

I

[Legend]

H = Host control, SL = Slave control, R = Recovery, T = Turnaround, S = Sample

[Legend]

H = Host control, R = Recovery, T = Turnaround, S = Sample, I = Idle

Figure 15.6 SERIRQ Timing

The serialized interrupt transfer cycle frame configuration is as follows. Two of the states

comprising each frame are the recover state in which the SERIRQ signal is returned to the 1-level

at the end of the frame, and the turnaround state in which the SERIRQ signal is not driven. The

recover state must be driven by the host or slave processor that was driving the preceding state.