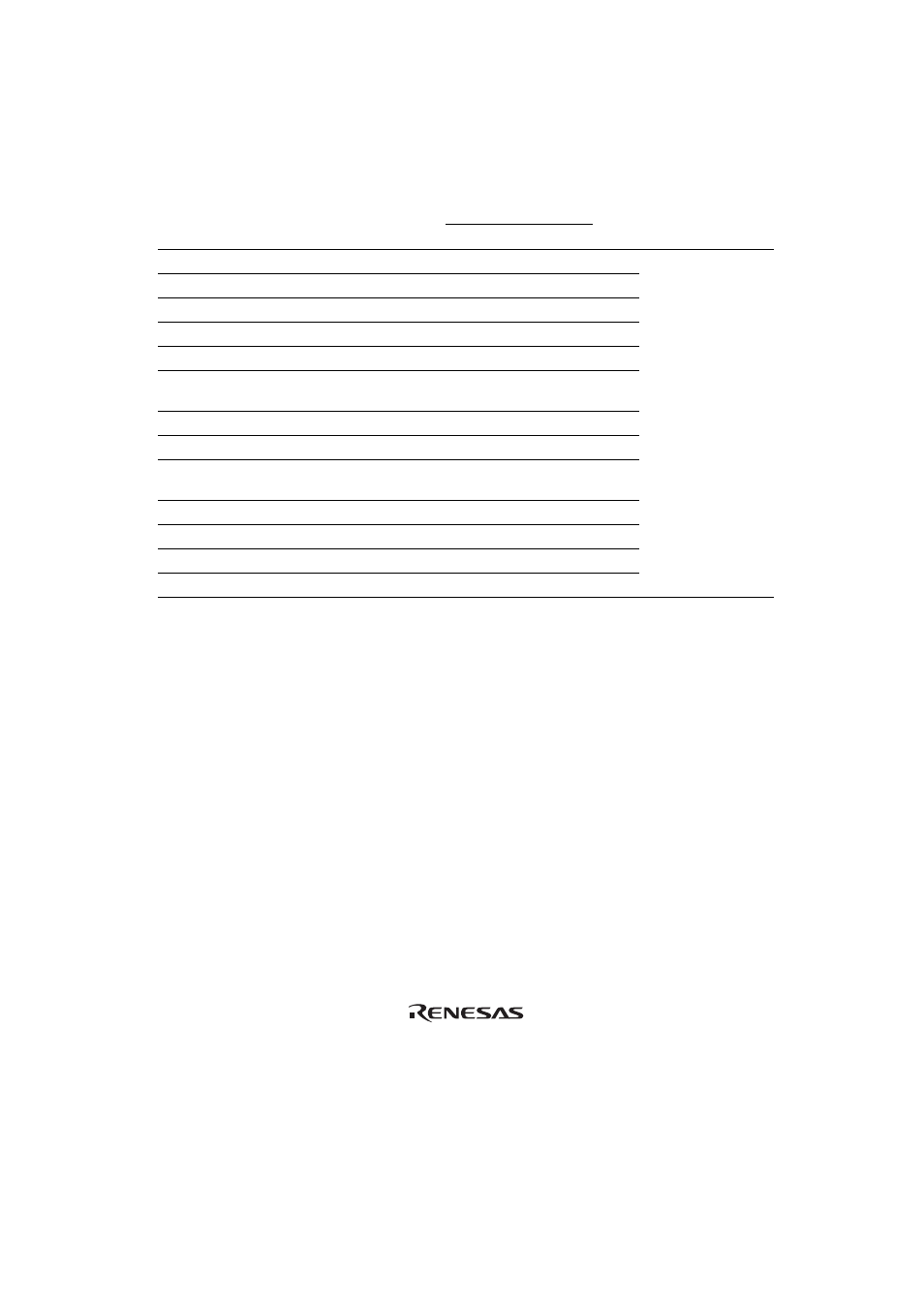

Table 22.9 i, C bus timing conditions: v, 0 v to 3.6 v, v – Renesas H8S/2111B User Manual

Page 559: 0 v, φ = 5 mhz to maximum operating frequency, t, 20 to +75°c

Rev. 1.00, 05/04, page 525 of 544

Table 22.9 I

2

C Bus Timing

Conditions: V

CC

= 3.0 V to 3.6 V, V

SS

= 0 V,

φ = 5 MHz to maximum operating frequency,

T

a

= –20 to +75°C

Ratings

Item Symbol

Min.

Typ.

Max.

Unit

Test

Conditions Notes

SCL input cycle time

t

SCL

12 — — t

cyc

SCL input high pulse width

t

SCLH

3 — — t

cyc

SCL input low pulse width

t

SCLL

5 — — t

cyc

SCL, SDA input rise time

t

Sr

—

—

7.5*

t

cyc

SCL, SDA input fall time

t

Sf

—

—

300

ns

SCL, SDA input spike pulse

elimination time

t

SP

—

—

1

t

cyc

SDA input bus free time

t

BUF

5 — — t

cyc

Start condition input hold time

t

STAH

3 — — t

cyc

Retransmission start condition

input setup time

t

STAS

3 — — t

cyc

Stop condition input setup time

t

STOS

3 — — t

cyc

Data input setup time

t

SDAS

0.5 — — t

cyc

Data input hold time

t

SDAH

0 — — ns

SCL, SDA capacitive load

C

b

—

—

400

pF

Figure

22.22

Note: * 17.5

t

cyc

can be set according to the clock selected for use by the I

2

C module. For

details, see section 13.6, Usage Notes.