3 erase block registers 1 and 2 (ebr1, ebr2) – Renesas H8S/2111B User Manual

Page 474

Rev. 1.00, 05/04, page 440 of 544

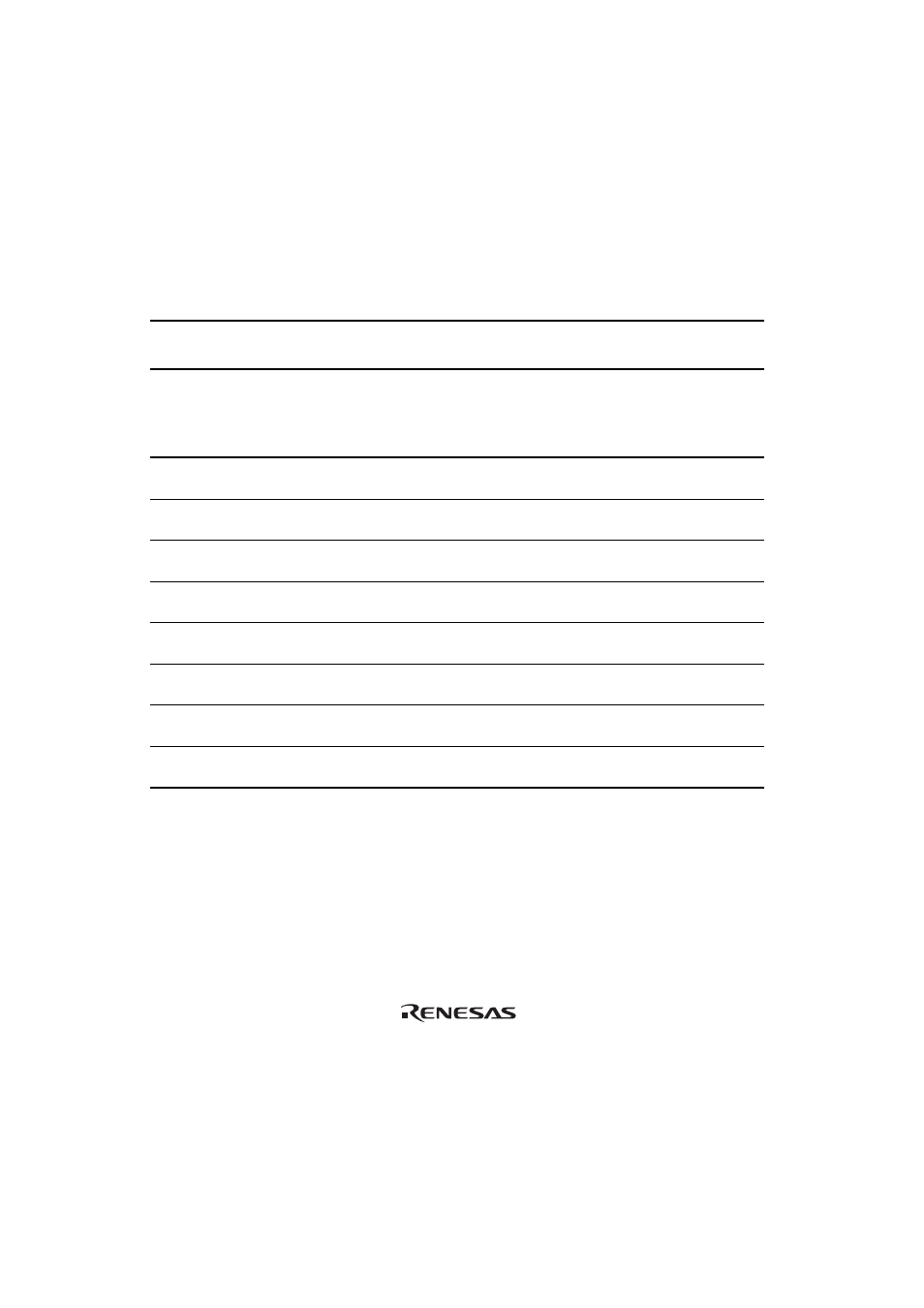

18.5.3

Erase Block Registers 1 and 2 (EBR1, EBR2)

EBR1 and EBR2 are used to specify the flash memory erase block. EBR1 and EBR2 are

initialized to H'00 by a reset, or in hardware standby mode, software standby mode, sub-active

mode, sub-sleep mode, or watch mode, or when the SWE bit in FLMCR1 is cleared to 0. Set only

one bit to 1 at a time, otherwise all bits in EBR1 and EBR2 are automatically cleared to 0.

• EBR1

Bit Bit

Name

Initial

Value R/W Description

7 to 0

—

All 0

R/(W)

Reserved

The initial values should not be modified.

• EBR2

Bit Bit

Name

Initial

Value R/W Description

7 EB7

0 R/W*

When this bit is set to 1, 8 Kbytes of EB7

(H'00E000 to H'00FFFF) are to be erased.

6

EB6

0

R/W

When this bit is set to 1, 8 Kbytes of EB6

(H'00C000 to H'00DFFF) are to be erased.

5

EB5

0

R/W

When this bit is set to 1, 16 Kbytes of EB5

(H'008000 to H'00BFFF) are to be erased.

4

EB4

0

R/W

When this bit is set to 1, 28 Kbytes of EB4

(H'001000 to H'007FFF) are to be erased.

3

EB3

0

R/W

When this bit is set to 1, 1 Kbyte of EB3

(H'000C00 to H'000FFF) is to be erased.

2

EB2

0

R/W

When this bit is set to 1, 1 Kbyte of EB2

(H'000800 to H'000BFF) is to be erased.

1

EB1

0

R/W

When this bit is set to 1, 1 Kbyte of EB1

(H'000400 to H'0007FF) is to be erased.

0

EB0

0

R/W

When this bit is set to 1, 1 Kbyte of EB0

(H'000000 to H'0003FF) is to be erased.

Note: * In normal mode, this bit is always read as 0 and cannot be modified.