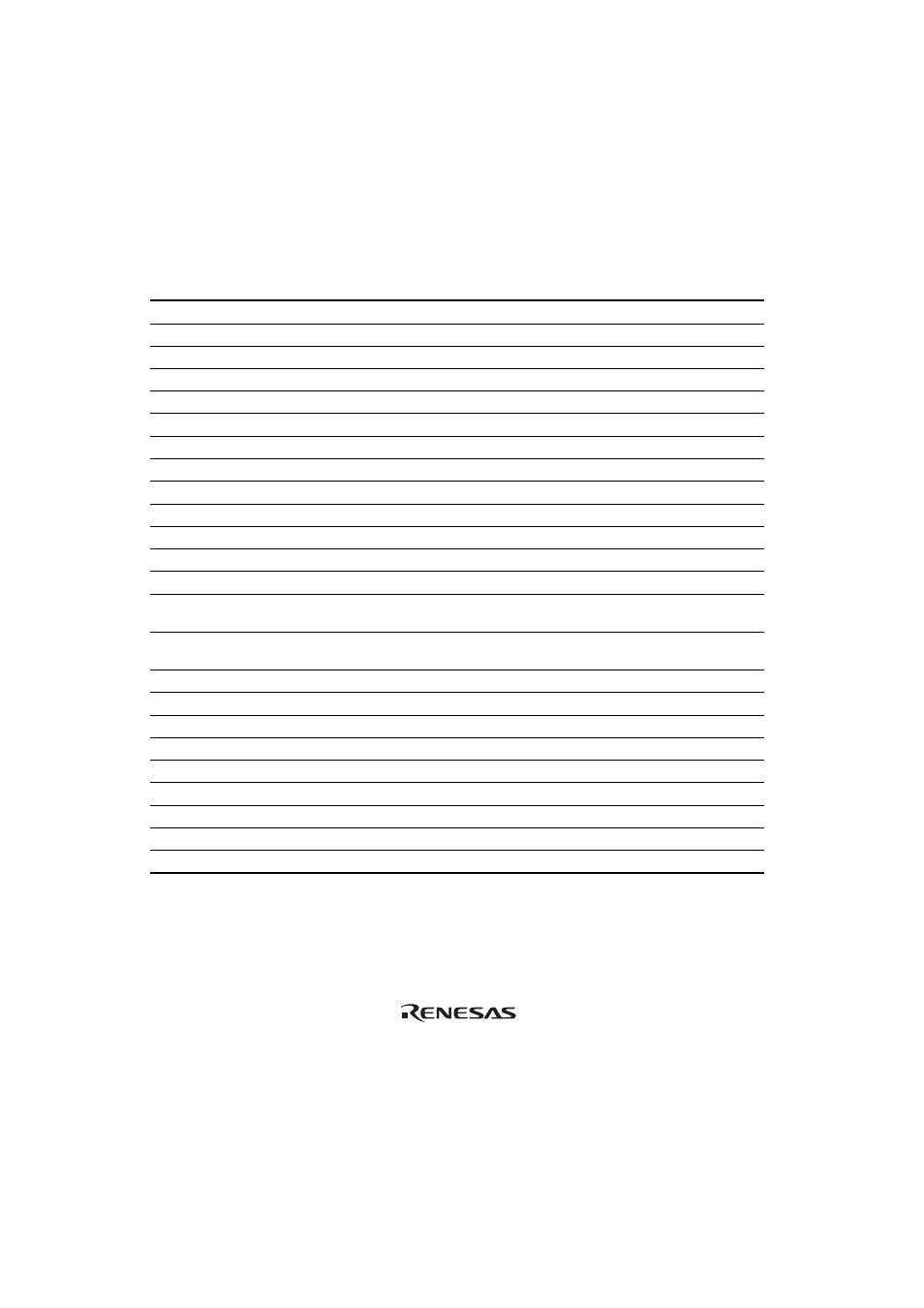

1 register addresses (address order) – Renesas H8S/2111B User Manual

Page 514

Rev. 1.00, 05/04, page 480 of 544

21.1

Register Addresses (Address Order)

The data bus width indicates the numbers of bits by which the register is accessed.

The number of access states indicates the number of states based on the specified reference clock.

Register Name

Abbreviation

Number

of Bits

Address

Module

Data

Bus

Width

Number

of

Access

States

Timer control register_B

TCR_B

8

H'FE00

TMR_B

8

3

Timer control register_A

TCR_A

8

H'FE01

TMR_A

8

3

Timer control/status register_B TCSR_B 8 H'FE02

TMR_B

8

3

Timer control/status register_A TCSR_A 8 H'FE03

TMR_A

8

3

Time constant register A_B

TCORA_B

8

H'FE04

TMR_B

8

3

Time constant register A_A

TCORA_A

8

H'FE05

TMR_A

8

3

Time constant register B_B

TCORB_B

8

H'FE06

TMR_B

8

3

Time constant register B_A

TCORB_A

8

H'FE07

TMR_A

8

3

Timer counter_B

TCNT_B

8

H'FE08

TMR_B

8

3

Timer counter_A

TCNT_A

8

H'FE09

TMR_A

8

3

Timer input select register_B

TISR_B

8

H'FE0A

TMR_B

8

3

Input capture register R_A

TICRR_A

8

H'FE0C

TMR_A

8

3

Input capture register F_A

TICRF_A

8

H'FE0D

TMR_A

8

3

Timer AB control register

TCRAB

8

H'FE0E

TMR_A,

TMR_B

8 3

Timer XY control register* TCRXY

8

H'FE10

TMR_X,

TMR_Y

8 3

Serial pin select register* SPSR

8

H'FE12

SCI_1

8

3

Port G control register* PGCTL

8

H'FE14

IIC

common

8

3

Port G open drain control register

PGNOCR

8

H'FE16

PORT

8

3

Port E open drain control register

PENOCR

8

H'FE18

PORT

8

3

Port F open drain control register

PFNOCR

8

H'FE19

PORT

8

3

Port C open drain control register PCNOCR 8

H'FE1C

PORT 8 3

Port D open drain control register PDNOCR 8

H'FE1D

PORT 8 3

Bidirectional data register 0MW TWR0MW

8 H'FE20

LPC 8 3

Bidirectional data register 0SW TWR0SW

8 H'FE20

LPC 8 3