6 serial data reception (asynchronous mode) – Renesas H8S/2111B User Manual

Page 290

Rev. 1.00, 05/04, page 256 of 544

12.4.6

Serial Data Reception (Asynchronous Mode)

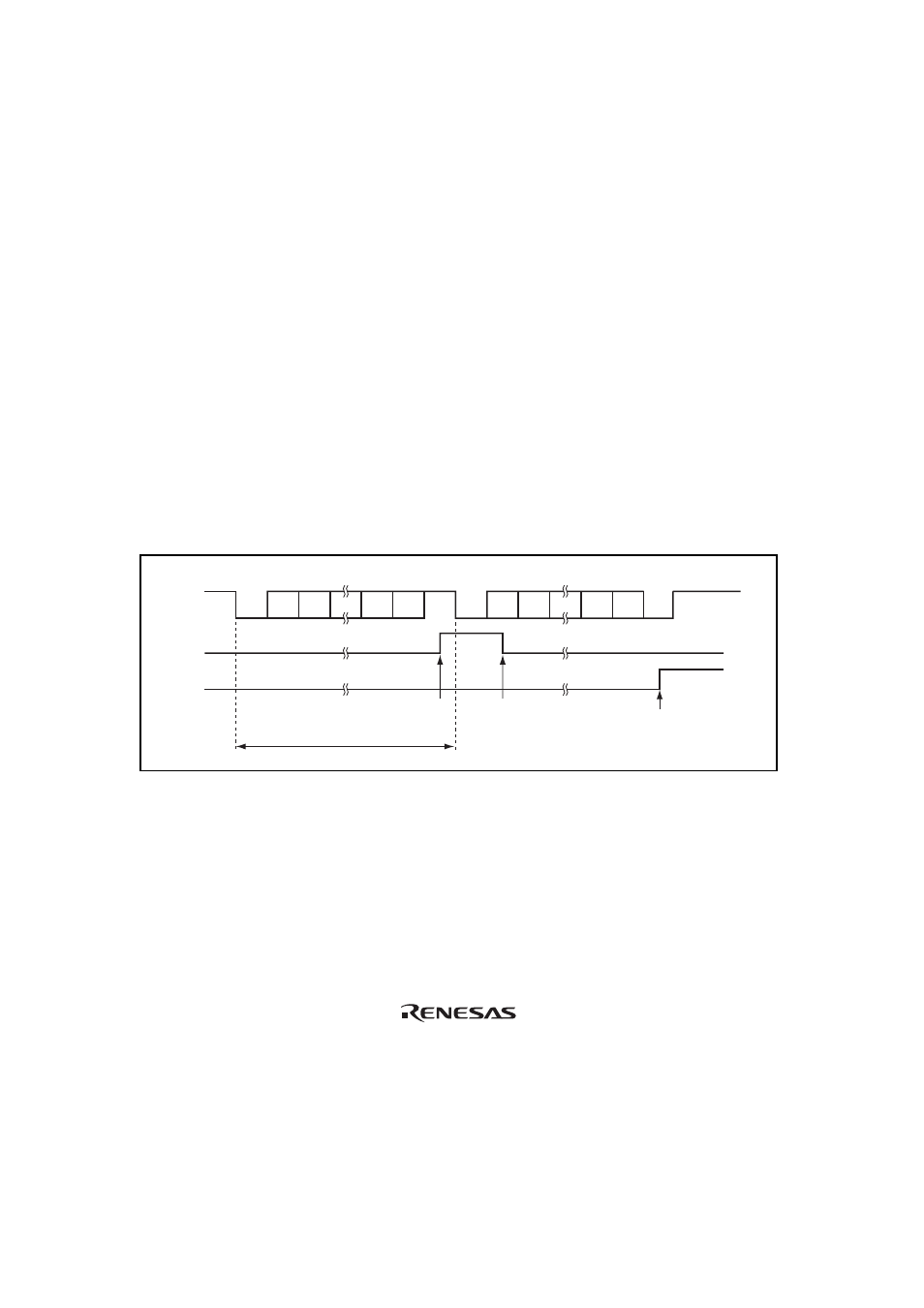

Figure 12.8 shows an example of the operation for reception in asynchronous mode. In serial

reception, the SCI operates as described below.

1. The SCI monitors the communication line, and if a start bit is detected, performs internal

synchronization, receives receive data in RSR, and checks the parity bit and stop bit.

2. If an overrun error (when reception of the next data is completed while the RDRF flag in SSR

is still set to 1) occurs, the ORER bit in SSR is set to 1. If the RIE bit in SCR is set to 1 at this

time, an ERI interrupt request is generated. Receive data is not transferred to RDR. The RDRF

flag remains to be set to 1.

3. If a parity error is detected, the PER bit in SSR is set to 1 and receive data is transferred to

RDR. If the RIE bit in SCR is set to 1 at this time, an ERI interrupt request is generated.

4. If a framing error (when the stop bit is 0) is detected, the FER bit in SSR is set to 1 and receive

data is transferred to RDR. If the RIE bit in SCR is set to 1 at this time, an ERI interrupt

request is generated.

5. If reception finishes successfully, the RDRF bit in SSR is set to 1, and receive data is

transferred to RDR. If the RIE bit in SCR is set to 1 at this time, an RXI interrupt request is

generated. Because the RXI interrupt routine reads the receive data transferred to RDR before

reception of the next receive data has finished, continuous reception can be enabled.

RDRF

FER

0

1 frame

D0

D1

D7

0/1

1

0

D0

D1

D7

0/1

0

1

1

Data

Start

bit

Parity

bit

Stop

bit

Start

bit

Data

Parity

bit

Stop

bit

ERI interrupt request

generated by framing

error

Idle state

(mark state)

RDR data read and RDRF

flag cleared to 0 in RXI

interrupt handling routine

RXI interrupt

request

generated

Figure 12.8 Example of SCI Receive Operation in Asynchronous Mode

(Example with 8-Bit Data, Parity, One Stop Bit)

Table 12.9 shows the states of the SSR status flags and receive data handling when a receive error

is detected. If a receive error is detected, the RDRF flag retains its state before receiving data.

Reception cannot be resumed while a receive error flag is set to 1. Accordingly, clear the ORER,

FER, PER, and RDRF bits to 0 before resuming reception. Figure 12.9 shows a sample flow chart

for serial data reception.