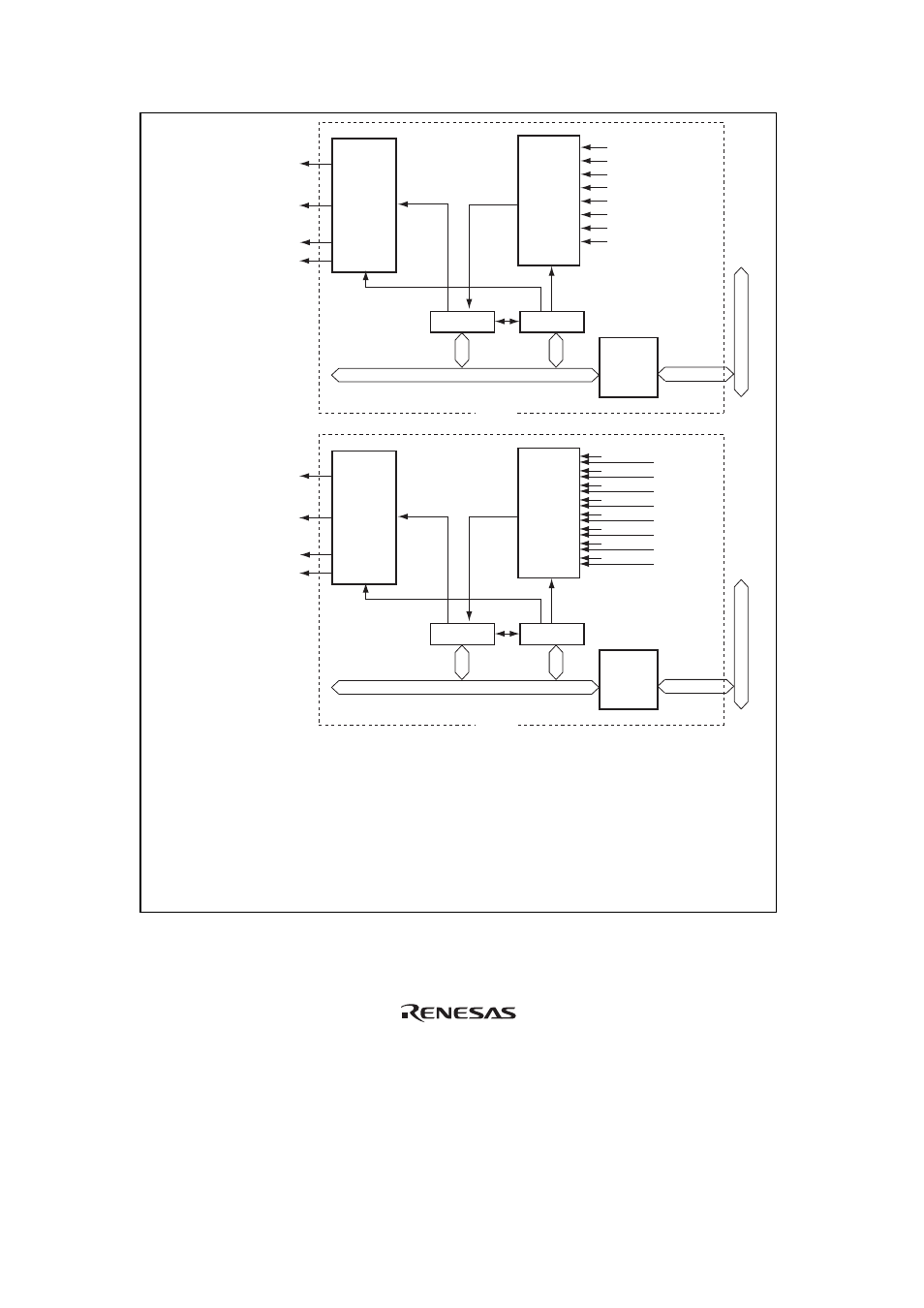

Figure 11.1 block diagram of wdt – Renesas H8S/2111B User Manual

Page 256

Rev. 1.00, 05/04, page 222 of 544

WOVI0

(Interrupt request signal)

Internal NMI

(Interrupt request signal*

2

)

RESO signal*

1

Internal reset signal*

1

TCNT_0

TCSR_0

φ/2

φ/64

φ/128

φ/512

φ/2048

φ/8192

φ/32768

φ/131072

Internal clock

Overflow

Interrupt

control

Reset

control

WOVI1

(Interrupt request signal)

Internal reset signal*

1

RESO signal*

1

TCNT_1

TCSR_1

φ/2

φ/64

φ/128

φ/512

φ/2048

φ/8192

φ/32768

φ/131072

Clock

Clock

selection

Internal clock

Bus

interface

Module bus

TCSR_0 : Timer control/status register_0

TCNT_0 : Timer counter_0

TCSR_1 : Timer control/status register_1

TCNT_1 : Timer counter_1

Notes: 1. The

RESO signal outputs the low level signal when the internal reset signal is

generated due to a TCNT overflow of either WDT_0 or WDT_1. The internal reset signal

first resets the WDT in which the overflow has occurred first.

2. The internal NMI interrupt signal can be independently output from either WDT_0 or WDT_1.

The interrupt controller does not distinguish the NMI interrupt request from WDT_0 from

that from WDT_1.

Internal bus

WDT_1

[Legend]

Internal NMI

(Interrupt request signal*

2

)

φSUB/2

φSUB/4

φSUB/8

φSUB/16

φSUB/32

φSUB/64

φSUB/128

φSUB/256

Overflow

Interrupt

control

Reset

control

Clock

Clock

selection

Bus

interface

Module bus

Internal bus

WDT_0

Figure 11.1 Block Diagram of WDT