6 slave transmit operation – Renesas H8S/2111B User Manual

Page 362

Rev. 1.00, 05/04, page 328 of 544

13.4.6

Slave Transmit Operation

If the slave address matches to the address in the first frame (address reception frame) following

the start condition detection when the 8th bit data (R/

W) is 1 (read), the TRS bit in ICCR is

automatically set to 1 and the mode changes to slave transmit mode.

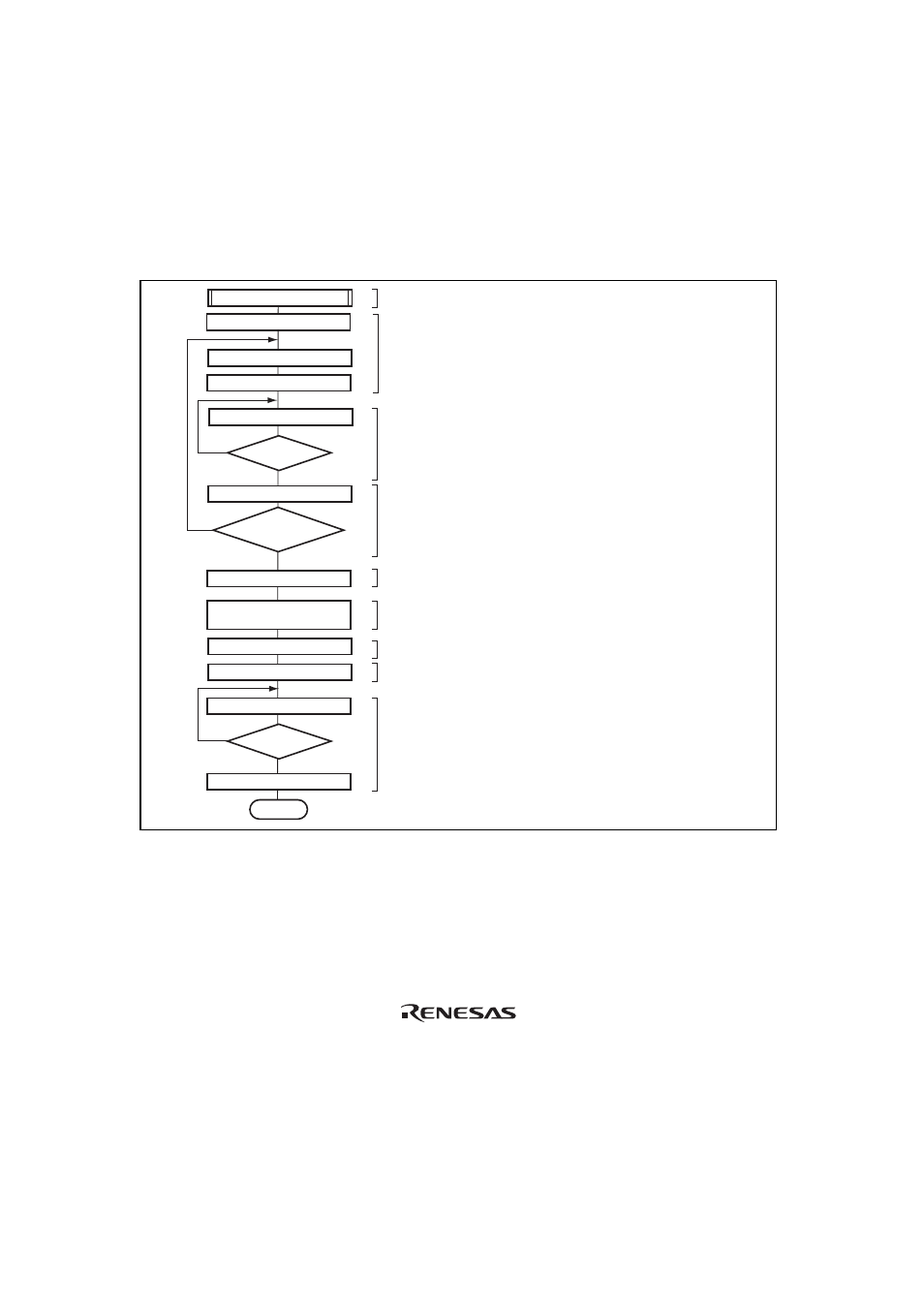

Figure 13.23 shows the sample flowchart for the operations in slave transmit mode.

End

Write transmit data in ICDR

Clear IRIC in ICCR

Clear IRIC in ICCR

Clear ACKE to 0 in ICCR

(ACKB=0 clear)

Clear IRIC in ICCR

Read IRIC in ICCR

Read ACKB in ICSR

Set TRS = 0 in ICCR

Read ICDR

Read IRIC in ICCR

IRIC = 1?

Yes

Yes

No

No

IRIC = 1?

Yes

No

[1], [2] If the slave address matches to the address in the first frame

following the start condition detection and the R/

W bit is 1

in slave recieve mode, the mode changes to slave transmit mode.

[8] Set slave receive mode.

[6] Read IRIC in ICCR

[7] Clear acknowledge bit data

[9] Dummy read (to release the SCL line).

[10]

Wait for stop condition

[3], [5] Set transmit data for the second and subsequent bytes.

[3], [4] Wait for 1 byte to be transmitted.

[4] Determine end of transfer.

Slave transmit mode

End

of transmission

(ACKB = 1)?

Clear IRIC in ICCR

Figure 13.23 Sample Flowchart for Slave Transmit Mode