11] commanded position no. output ready circuit – IAI America ERC3 User Manual

Page 428

Chapter 10

Appendix

10.5

Example of Basic Positioning Sequence (PIO Patterns 0 to 3 in PIO Converter)

418

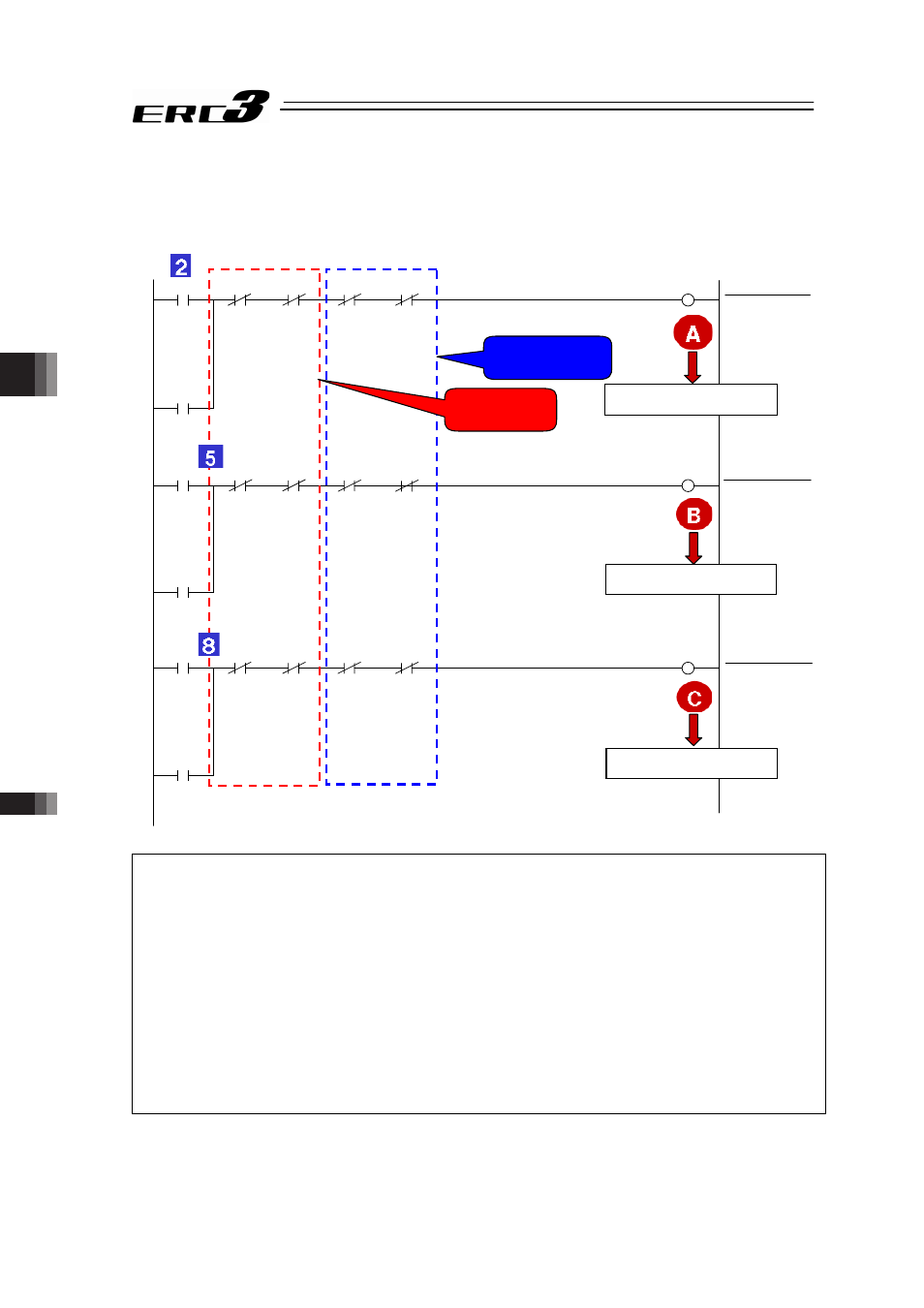

[11] Commanded Position No. Output Ready Circuit

The ready circuit is designed to hold start command and output commanded position No. in the

binary code.

Interlock is taken so that position No. command may not be specified incorrectly.

135

AUX18

142

AUX19

149

AUX20

a136 b146 b153

a156

Position 1 Set

b139 b143 b154

a159

Position 2 Set

b140 b147 a150

a157 a160

Position 3 Set

AUX9

Auxiliary

Position 1

Positioning

Start

AUX12

Auxiliary

Position 2

Positioning

Start

AUX15

Auxiliary

Position 3

Positioning

Start

AUX19

Position 2

Set

AUX20

Position 3

Set

AUX18

Position 2

Set

AUX12

Auxiliary

Position 2

Positioning

Start

AUX9

Auxiliary

Position 1

Positioning

Start

AUX15

Auxiliary

Position 3

Positioning

Start

AUX18

Position 1

Set

AUX20

Position 3

Set

AUX19

Position 2

Set

AUX15

Auxiliary

position 3

positioning

start

AUX9

Auxiliary

position 1

positioning

start

AUX12

Auxiliary

position 2

positioning

start

AUX18

Position 1

set

AUX19

Position 2

Set

AUX20

Position 3

Set

Position No.1, 2,

or 3 set relay

Position No.1, 2,

or 3 start command

To commanded position No.

output circuit

To commanded position No.

output circuit

To commanded position No.

output circuit

• Once a moving command to a position is issued, any of circuits A, B and C is turned ON to

remember it unless a moving command to another position is issued. The operation circuit is

cancelled by a stop command such as an emergency stop command. However, the circuit

remembers the positions to which the actuator moved and the positions at which the actuator

stopped until the cancellation. Such sequence design is also intended to cope with errors

occurred and helpful to find the causes of the errors from circuit status, stop position

inconsistency and other conditions.

• Taking interlock in both commands and results is usual means in circuit design to prevent results

from being ON simultaneously. For example, if both SOLs in a solenoid valve of double SOL

type are turned ON simultaneously, the coils are burned instantly. In another case, PLC

executes a program in descending order but operations are not always done in the order. If you

create a sequence program taking operation order into account, circuit change and/or addition

due to debugging and specification change may cause the operation order to be modified

without intention. Take interlock securely.