H3C Technologies H3C MSR 50 User Manual

Page 733

348

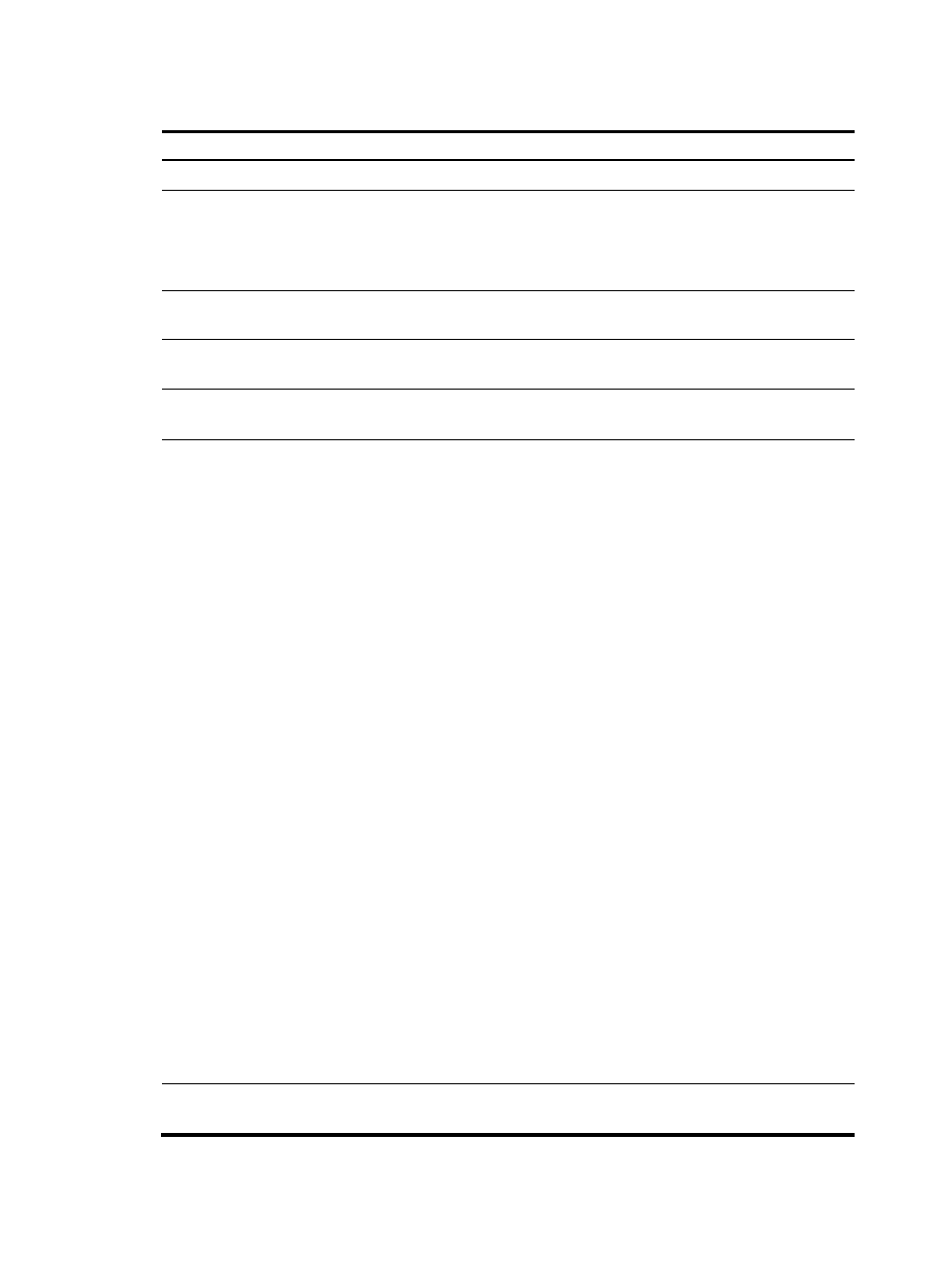

Table 270 Configuration items

Item Description

Physical Parameters Configuration

Working Mode

Configure the working mode of the T1 interface:

•

None—Remove the existing bundle.

•

PRI Trunk Signaling—Bundle timeslots on a T1 interface into a PRI group.

By default, no PRI group is created.

Bound Timeslot

Number

Specify the timeslots to be bundled.

Frame Check Mode

•

ESF—Perform extended super frame (ESF).

•

SF—Perform super frame (SF).

Line Coding

•

B8ZS—The line coding format is bipolar 8 zero substitution (B8ZS).

•

AMI—The line coding format is alternate mark inversion (AMI).

TDM Clock Source

•

Internal—Set the internal crystal oscillator TDM clock as the TDM clock source on

the T1 interface. After that, the T1 interface obtains clock from the crystal oscillator

on the main board. If it fails to do that, the interface obtains clock from the crystal

oscillator on its T1 card. Because SIC cards are not available with crystal

oscillator clocks, T1 interfaces on SIC cards can only obtain clock from the main

board. The internal clock source is also called master clock mode in some

features.

•

Line—Set the line TDM clock as the TDM clock source on the T1 interface. After

that, the T1 interface obtains clock from the remote device through the line. The

line clock source is called as slave clock mode in some features.

•

Line primary—Set the T1 interface to preferably use the line TDM clock as the

TDM clock source. After that, the T1 interface always attempts to use the line TDM

clock prior to any other clock sources.

By default, the TDM clock source for a T1 interface is the internal clock.

When digital voice T1 interfaces perform TDM timeslot interchange, it is important

for them to achieve clock synchronization to prevent frame slips and bit errors.

Depending on your configurations on T1 interfaces at the CLI, the system adopts

different clocking approaches. When there is a subcard VCPM on the main board,

the clock distribution principle is as follows:

•

If the line keyword is specified for all interfaces, the clock on the interface with the

lowest number is adopted. In case the interface goes down, the clock on the

interface with the next second number is adopted.

•

If line primary is specified for interface X and line or internal is specified for other

interfaces, the clock on interface X is adopted.

•

If line is specified for interface X and internal is specified for other interfaces, the

clock on interface X is adopted.

•

Generally, you cannot set the clock source for all interfaces in a system as internal

to prevent frame slips and bit errors. However, you can do this if the remote T1

interfaces adopt the line clock source.

When there is no VCPM on the main board, the configuration of each MIM/FIC is

independent but only one interface can be set as line primary.

Status

•

Enable—Enable the T1 interface.

•

Disable—Disable the T1 interface.

If you select the PRI Trunk Signaling option, the page as shown in

appears.