Memory system failure event sense data response, D–12 hsg80 user’s guide – HP Array Controller HSG V8.7 Software User Manual

Page 446

D–12

HSG80 User’s Guide

Memory System Failure Event Sense Data Response

The HSG80 controller Memory Controller Event Analyzer software

component and the Cache Manager, part of the Value Added software

component, report the occurrence of memory errors via the Memory

System Failure Event Sense Data Response (see Figure D–8).

n

Instance Codes (byte offset 32-35) are described in Table D–1,

“Instance Codes” on page D–18.

n

ASC and ASCQ codes (byte offsets 12 and 13) are described in

Table D–7, “ASC and ASCQ Codes” on page D–85.

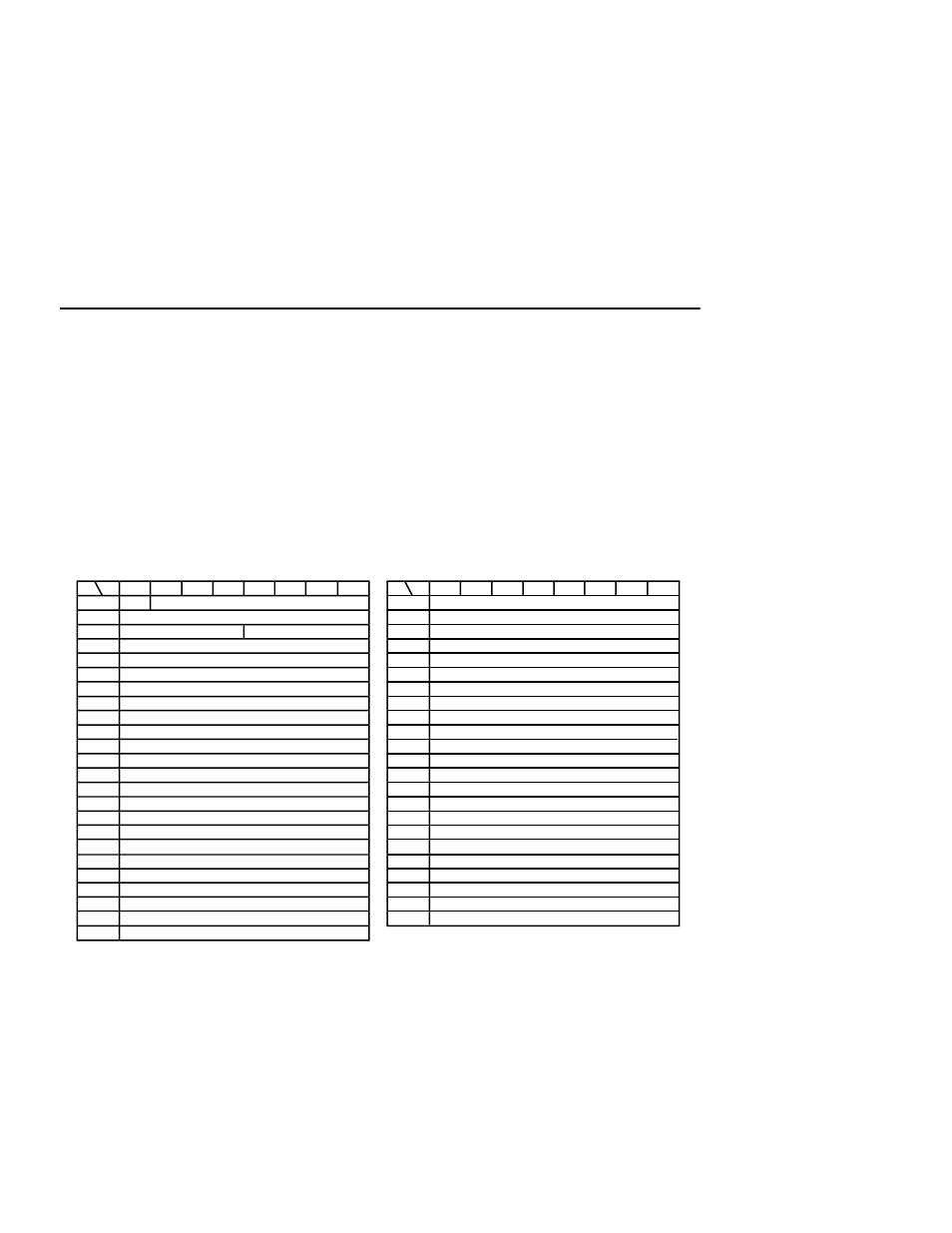

Figure D–8 Template 14 - Memory System Failure Event Sense Data Response Format

off

bit

7

6

5

4

3

2

1

Unusd

Unused

Unused

Unused

Unused

Error Code

0

1

2

3-6

7

8-11

12

13

14

15-17

18-19

20-23

24-27

28-31

32–35

36

37

38-39

40-43

44-47

48-51

52-53

54-69

70-73

0

Sense Key

Additional Sense Length

Additional Sense Code (ASC)

Additional Sense Code Qualifier (ASCQ)

Reserved

Reserved or RDEAR (TM1)

Template

Reserved or RDR2 (TM1)

Reserved

Instance Code

Template Flags

Reserved

Reserved or FXPSCR (TM1)

Reserved or FXCSR (TM1)

Reserved or FXCCSR (TM1)

Reserved

Unused

off

bit

7

6

5

4

3

2

1

LUN Status

74-75

76

77-79

80-83

84-87

88-91

92-95

96-99

100-103

104-107

108-111

112-115

116-119

120-123

124-127

128-131

132-135

136-139

140-143

144-147

148-151

152-155

156-159

0

Reserved

Reserved or CHC (TM0) or FXCAEP(TM1)

Memory Address

Reserved or FXCAEC(TM1)

Reserved or FXPAEP(TM1)

Reserved or CMC (TM0) or CFW(TM1)

Reserved or DSR2 (TM0) or RRR(TM1)

DSR or PSR(TM1)

CSR or CSR(TM1)

DCSR or EAR(TM1)

DER or EDR1(TM1)

EAR or EDR0(TM1)

EDR or ICR TM1)

ERR or IMR(TM1)

RSR or DIO(TM1)

RDR0

RDR1

WDR0

WDR1

Controller Software Revision Level

Reserved

Byte Count

Reserved or FXPAEC(TM1)

Unused

Controller Board Serial Number

CXO6181A