Avago Technologies MegaRAID Fast Path Software User Manual

Page 17

LSI Corporation Confidential

|

July 2011

Page 17

MegaRAID SAS Software User Guide

Chapter 1: Overview

|

Configuration Scenarios

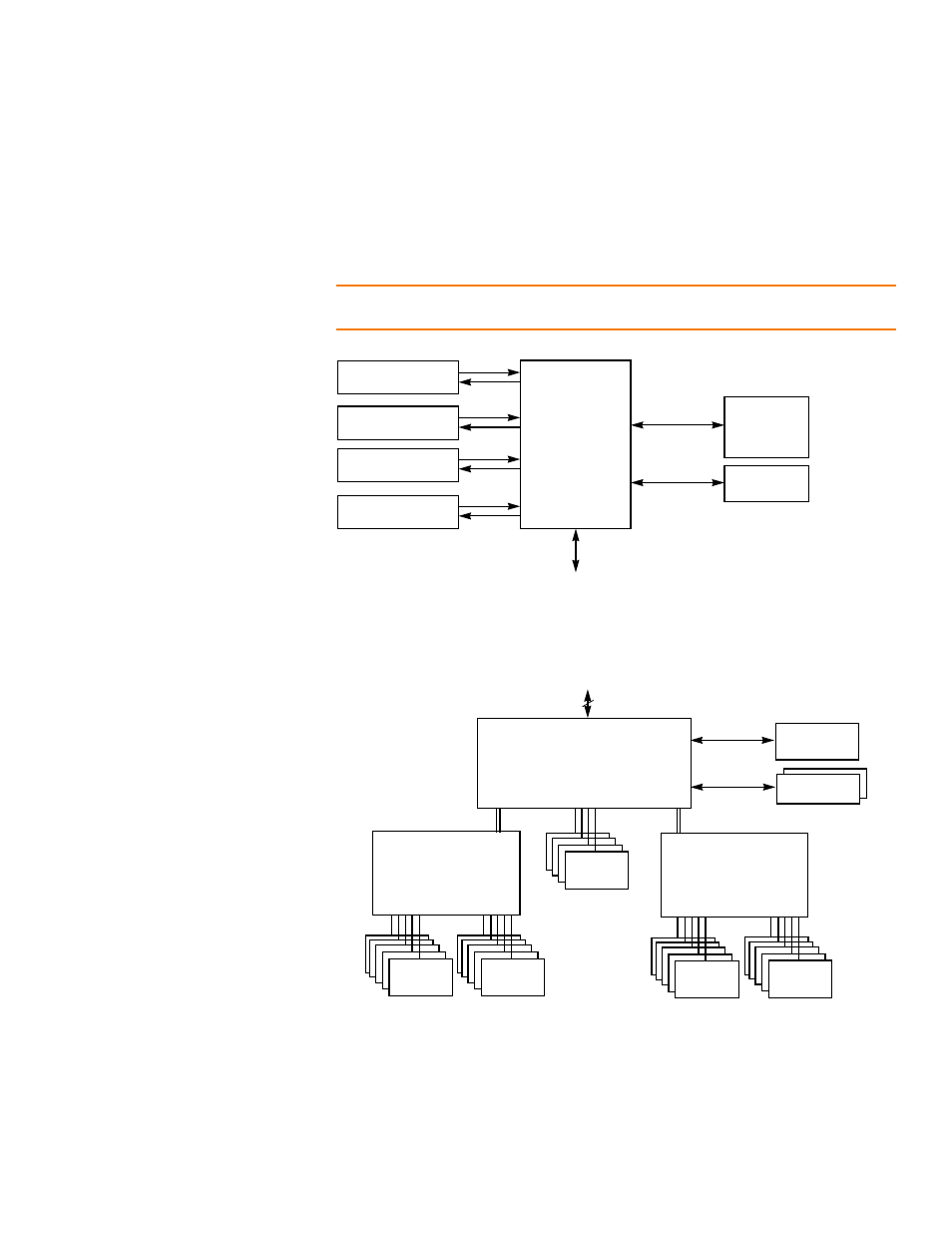

shows a direct-connect configuration. The Inter-IC (I

2

C) interface

communicates with peripherals. The external memory bus provides a 32-bit memory

bus, parity checking, and chip select signals for pipelined synchronous burst static

random access memory (PSBRAM), nonvolatile static random access memory

(NVSRAM), and Flash ROM.

NOTE: The external memory bus is 32-bit for the SAS 8704ELP and the SAS 8708ELP,

and 64-bit for the SAS 8708EM2, the SAS 8880EM2, and the SAS 8888ELP.

Figure 1:

Example of an LSI SAS Direct-Connect Application

shows an example of a SAS RAID controller configured with an LSISASx12

expander that is connected to SAS disks, SATA II disks, or both.

Figure 2:

Example of an LSI SAS RAID Controller Configured with an LSISASx12

Expander

Flash ROM/

SAS

PCI Express

RAID Controller

SAS/SATA II Device

32-Bit Memory

Address/Data

Bus

PSBRAM/

I

2

C

SAS/SATA II Device

SAS/SATA II Device

SAS/SATA II Device

PCI Express Interface

NVSRAM

I

2

C

Interface

LSISASx12

Flash ROM/

NVSRAM/

SRAM

I

2

C/UART

LSISASx12

SAS/SATA II

Drives

PCI Express Interface

SAS/SATA

Drives

SAS/SATA II

Drives

SAS/SATA II

Drives

SAS/SATA II

Drives

8

SRAM

SRAM

SDRAM

Peripheral

Bus

72-bit DDR/DDR2

with ECC

Interface

LSISAS1078

PCI Express to SAS ROC

SAS RAID Controller

Expander

Expander

- MegaRAID SAS 9240-4i MegaRAID SAS 9240-8i MegaRAID SAS 9260-16i MegaRAID SAS 9260-4i MegaRAID SAS 9260-8i MegaRAID SAS 9261-8i MegaRAID SAS 9280-16i4e MegaRAID SAS 9280-4i4e MegaRAID SAS 9280-8e MegaRAID SafeStore Software MegaRAID SAS 9361-4i MegaRAID SAS 9361-8i MegaRAID SAS 9266-4i MegaRAID SAS 9266-8i MegaRAID SAS 9270-8i MegaRAID SAS 9271-4i MegaRAID SAS 9271-8i MegaRAID SAS 9271-8iCC MegaRAID SAS 9286-8e MegaRAID SAS 9286CV-8e MegaRAID SAS 9286CV-8eCC MegaRAID CacheCade Pro 2.0 Software MegaRAID SAS 9341-4i MegaRAID SAS 9341-8i MegaRAID SAS 9380-8e MegaRAID SAS 9380-4i4e