2 hardware multiplier operation – Texas Instruments MSP430x1xx User Manual

Page 91

Hardware Multiplier Operation

6-3

Hardware Multiplier

6.2

Hardware Multiplier Operation

The hardware multiplier has two 16-bit registers for both operands and three

registers to store the results of the multiplication. The multiplication is

executed correctly when the first operand is written to the operand register

OP1 prior to writing the second operand to OP2. Writing the first operand to

the applicable register selects the type of multiplication. Writing the second

operand to OP2 starts the multiplication. Multiplication is completed before the

result registers are accessed using the indexed address mode for the source

operand. When indirect or indirect autoincrement address modes are used,

another instruction is needed between the writing of the second operand and

accessing the result registers. Both operands, OP1 and OP2, utilize all seven

address mode capabilities.

No instruction is necessary for the multiplication; as a result, the real-time

operation does not require additional clock cycles and the interrupt latency is

unchanged.

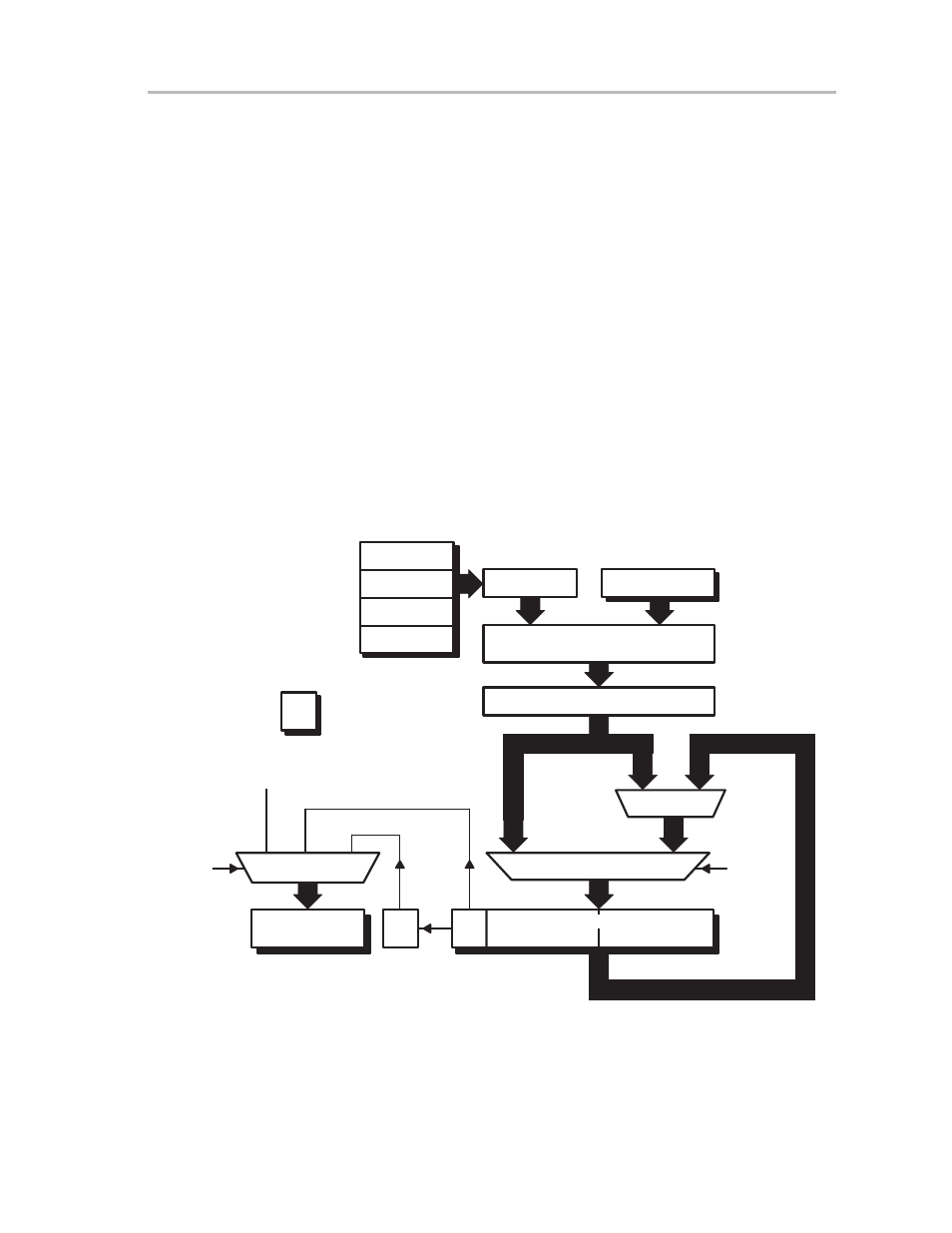

The multiplier architecture is illustrated in Figure 6–2.

Figure 6–2. Block Diagram of the MSP430 16

×

16-Bit Hardware Multiplier

MAC, MACS

MPY 130h

MACS 136h

MAC 134h

MPYS 132h

Operand 1

Operand 2 138h

Product Register

16 x 16 Multiplier

32-Bit Adder

32-Bit Multiplexer

Accumulator ACC

SumExt 13Eh

C

Multiplexer

SumLo 013Ah

SumHi 13Ch

S

Operand 1

(address

defines

operation)

0

rw

15

0

rw

15

0

rw

15

0

31

0

rw

15

0

rw

15

0

r

15

0000

MACS

MPYS

MAC

MPY

Accessible Register

Mode

Mode

MPY, MPYS

Mode