Texas Instruments MSP430x1xx User Manual

Page 154

Timer Modes

10-14

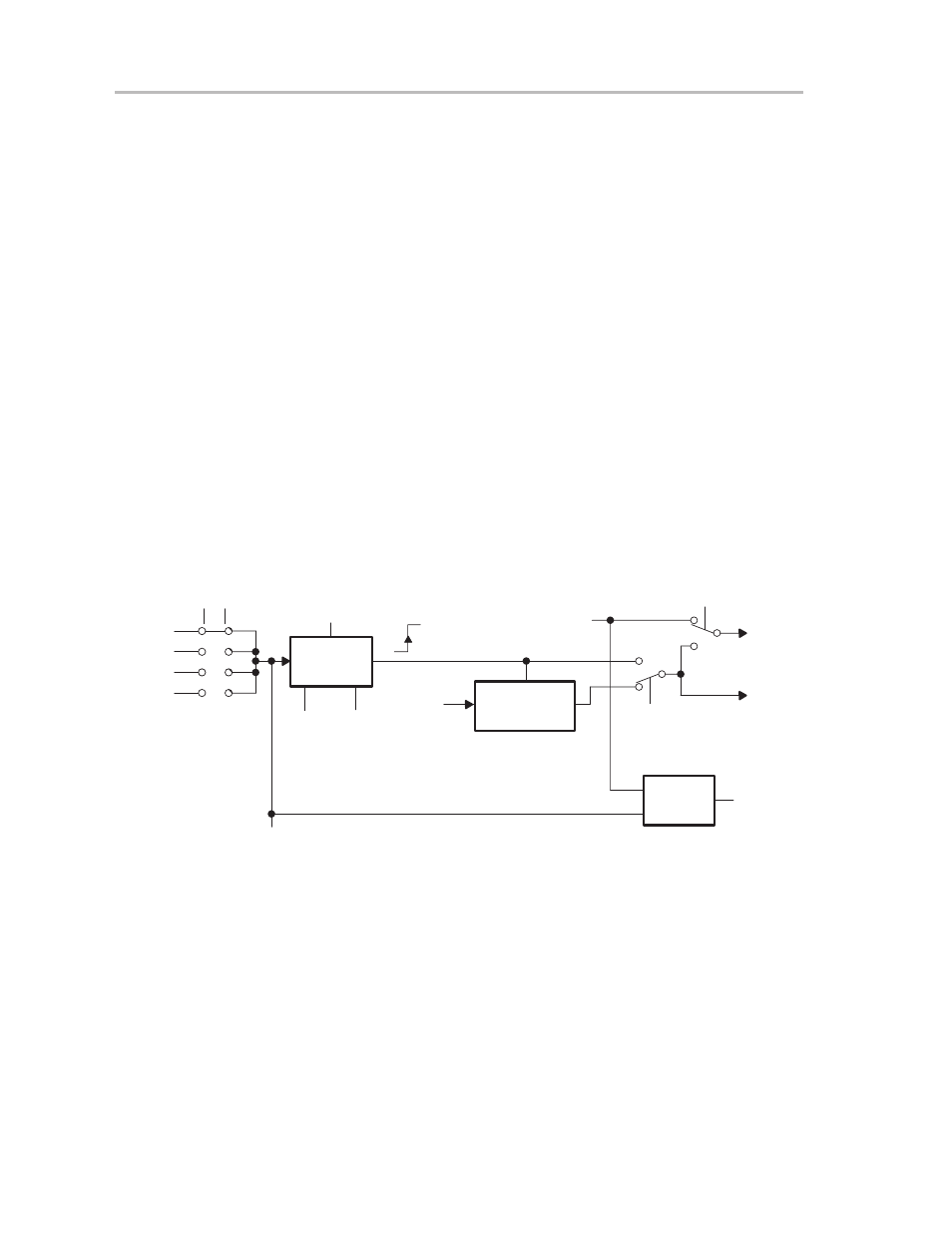

10.4.1 Capture/Compare Block—Capture Mode

The capture mode is selected if the mode bit CAPx, located in control word

CCTLx, is set. The capture mode is used to fix time events. It can be used for

speed computations or time measurements. The timer value is copied into the

capture register (CCRx) with the selected edge (positive, negative, or both) of

the input signal. Captures may also be initiated by software as described in

section 10.4.1.1.

If a capture is performed:

-

The interrupt flag CCIFGx, located in control word CCTLx, is set.

-

An interrupt is requested if both interrupt enable bits CCIEx and GIE are

set.

The input signal to the capture/compare block is selected using control bits

CCISx1 and CCISx0, as shown in Figure 10–18. The input signal can be read

at any time by the software by reading bit CCIx. The input signal may also be

latched with compare signal EQUx (see SCCIx bit below) when in compare

mode. This feature was designed specifically to support implementing serial

communications with Timer_A. See section 10.7 for more details on using

Timer_A as a UART.

Figure 10–18. Capture Logic Input Signal

Capture

Mode

EN

CCISx0

CCISx1

CCIxA

CCIxB

GND

0

1

2

3

V

CC

CCMx1 CCMx0

Set_CCIFGx

0

0

1

1

0

1

0

1

Disabled

Positive Edge

Negative Edge

Both Edges

1

0

CAPx

A

Y

CCIx

SCCIx

EQUx

CMPx

Synchronize

Capture

Timer

Clock

0

1

Capture

SCSx

The capture signal can also be synchronized with the timer clock to avoid race

conditions between the timer data and the capture signal. This is illustrated in

Figure 10–19. The bit SCSx in capture/compare control register CCTLx

selects the capture signal synchronization.