Texas Instruments MSP430x1xx User Manual

Page 80

Addressing Modes

5-16

5.2.8.2

Format-II Instructions

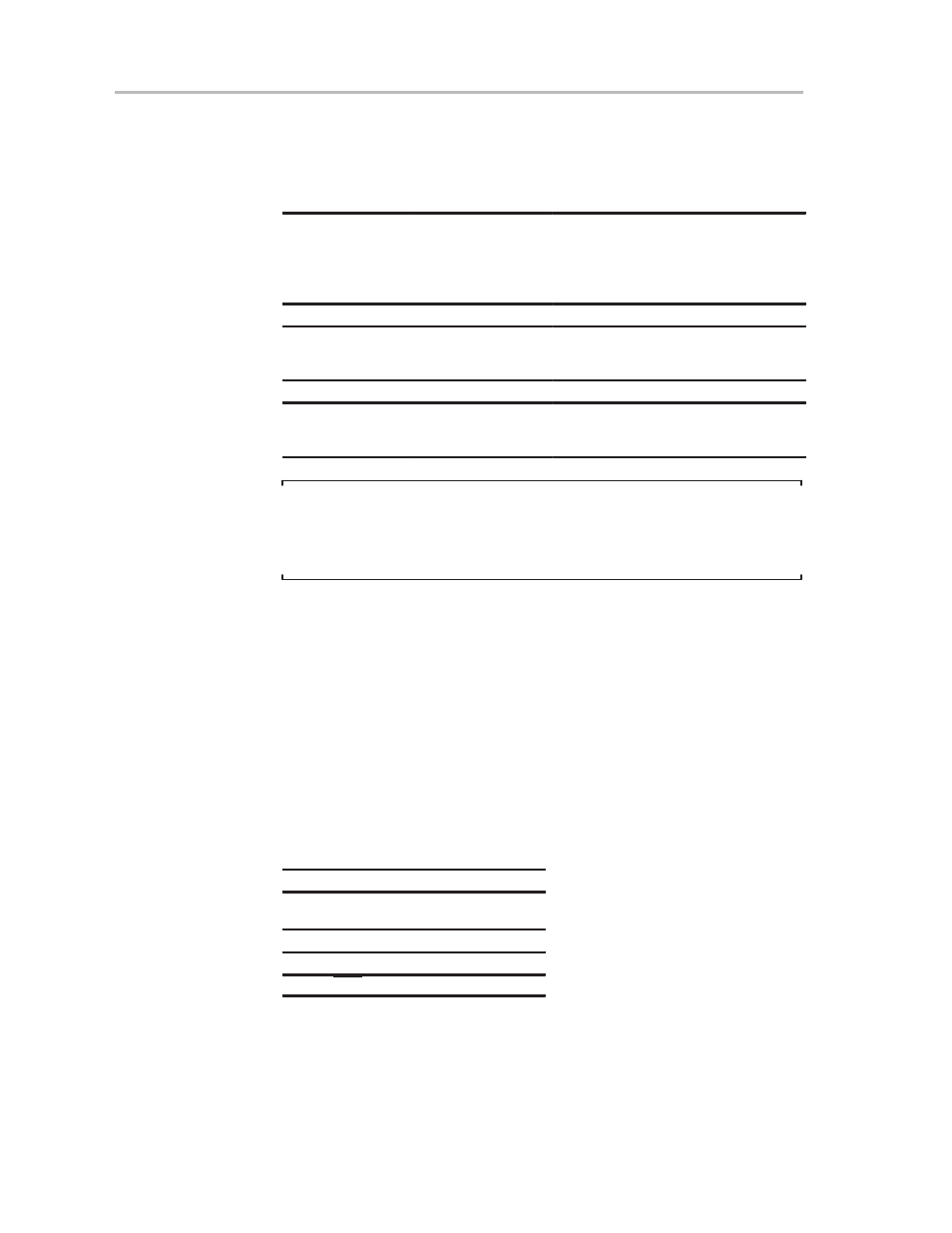

Table 5–13 describes the CPU format II instructions and addressing modes.

Table 5–13.Instruction Format-II and Addressing Modes

No. of Cycles

Address Mode

A

(s/d)

RRA

RRC

SWPB

SXT

PUSH/

CALL

Length of

Instruction

(words)

Example

00, Rn

1

3/4

1

SWPB R5

01, X(Rn)

01, EDE

01, &EDE

4

4

5

5

2

2

CALL 2(R7)

PUSH EDE

SXT &EDE

10, @Rn

3

4

1

RRC @R9

11, @Rn+

(see Note)

11, #N

3

4/5

1

2

SWPB @R10+

CALL #81H

Note:

Instruction Format II Immediate Mode

Do not use instructions RRA, RRC, SWPB, and SXT with the immediate

mode in the destination field. Use of these in the immediate mode will result

in an unpredictable program operation.

5.2.8.3

Format-III Instructions

Format-III instructions are described as follows:

Jxx—all instructions need the same number of cycles, independent of

whether a jump is taken or not.

Clock cycle:

Two cycles

Length of instruction:

One word

5.2.8.4

Miscellaneous-Format Instructions

Table 5–14 describes miscellaneous-format instructions.

Table 5–14.Miscellaneous Instructions or Operations

Activity

Clock Cycle

RETI

5 cycles

1 word

†

Interrupt

6 cycles

WDT reset

4 cycles

Reset (RST/NMI)

4 cycles

† Length of instruction