Texas Instruments MSP430x1xx User Manual

Page 38

MSP430 Interrupt-Priority Scheme

3-8

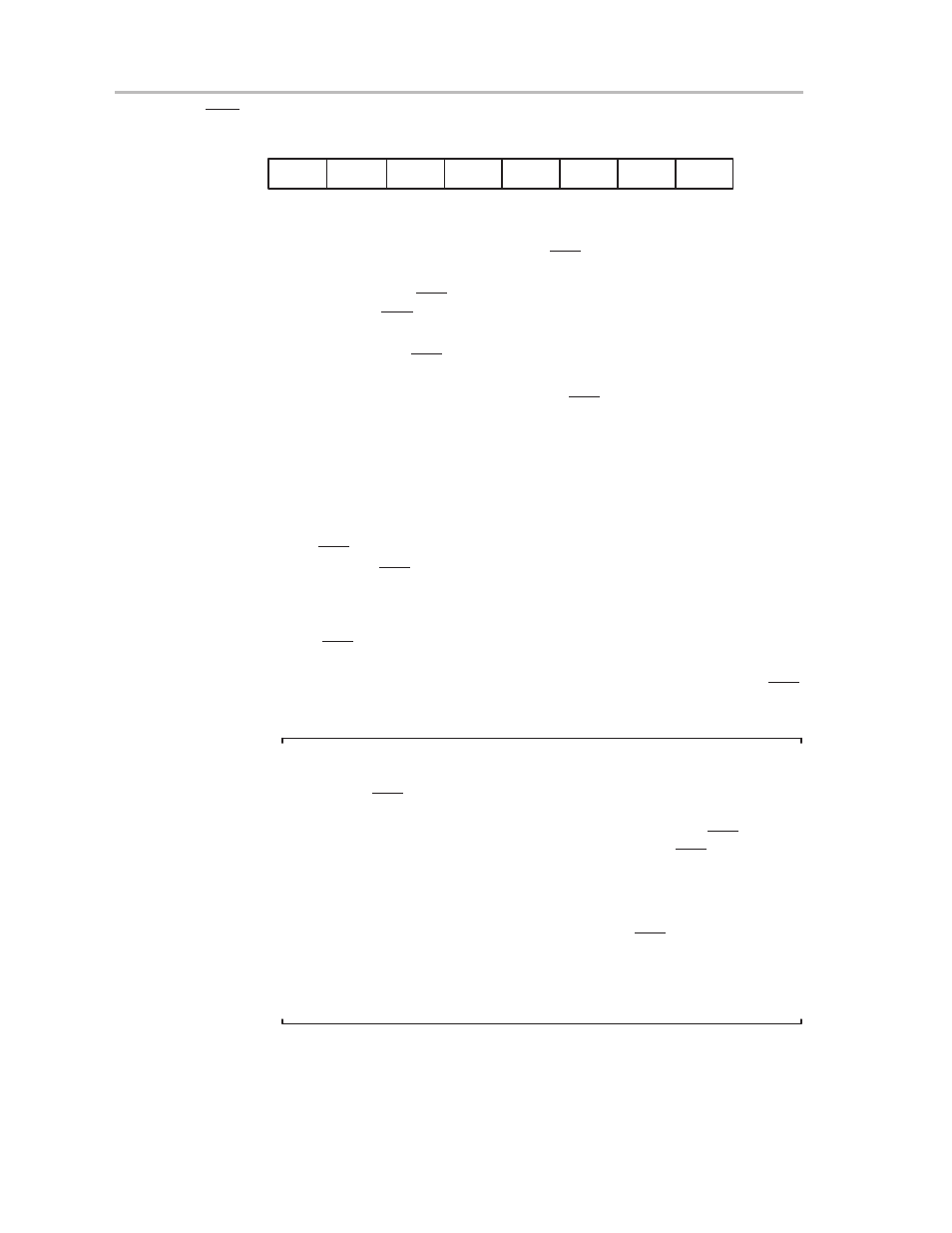

Figure 3–6. RST/NMI Mode Selection

NMIES

HOLD

NMI

TMSEL CNTCL

SSEL

IS1

IS0

WDTCTL

0120h

rw-0

rw-0

rw-0

rw-0

(w)-0

rw-0

rw-0

rw-0

7

0

BITS 0–4,7

See Watchdog Timer chapter.

BIT 5:

The NMI bit selects the function of the RST/NMI input pin. It is cleared after

a PUC signal.

NMI = 0:

The RST/NMI input works as reset input. As long as the

RST/NMI pin is held low, the internal PUC signal is active

(level-sensitive).

NMI = 1:

The RST/NMI input works as an edge-sensitive, nonmaskable

interrupt input.

BIT 6:

This bit selects the activating edge of the RST/NMI input if the NMI function

is selected. It is cleared after a PUC signal.

NMIES = 0: A rising edge triggers an NMI interrupt.

NMIES = 1: A falling edge triggers an NMI interrupt.

3.3.1

Operation of Global Interrupt—Reset/NMI

If the RST/NMI pin is set to the reset function, the CPU is held in the reset state

as long as the RST/NMI pin is held low. After the input changes to a high state,

the CPU starts program execution at the word address stored in word location

0FFFEh (reset vector).

If the RST/NMI pin is set to the NMI function, a signal edge (selected by the

NMIES bit) will generate an interrupt if the NMIIE bit is set. When accepted,

program execution begins at the address stored in location 0FFFCh. The RST/

NMI flag in the SFR IFG1.4 is also set.

Note:

When configured in the NMI mode, a signal generating an NMI event should

not hold the RST/NMI pin low, unless it is intended to hold the processor in

reset. When an NMI event occurs on the pin, the PUC signal is activated, thus

resetting the bits in the WDTCTL register. This results in the RST/NMI pin

being configured in the reset mode. If the signal on the RST/NMI pin that

generated the NMI event remains low, the processor will be held in the reset

state.

When NMI mode is selected and the NMI edge select bit is changed, an NMI

can be generated, depending on the actual level at RST/NMI pin. When the

NMI edge select bit is changed before selecting the NMI mode, no NMI is

generated.

The NMI interrupt is maskable by the NMIIE bit.