2 interrupt vector addresses – Texas Instruments MSP430x1xx User Manual

Page 45

Interrupt Processing

3-15

System Resets, Interrupts, and Operating Modes

3.4.2

Interrupt Vector Addresses

The interrupt vectors and the power-up starting address are located in the

ROM, using the address range 0FFFFh – 0FFE0h as described in Table 3–5.

The vector contains the 16-bit address of the appropriate interrupt handler

instruction sequence. The interrupt vectors for 14x devices are shown in Table

3–5 in decreasing order of priority. See device data sheet for interrupt vectors

for a specific device.

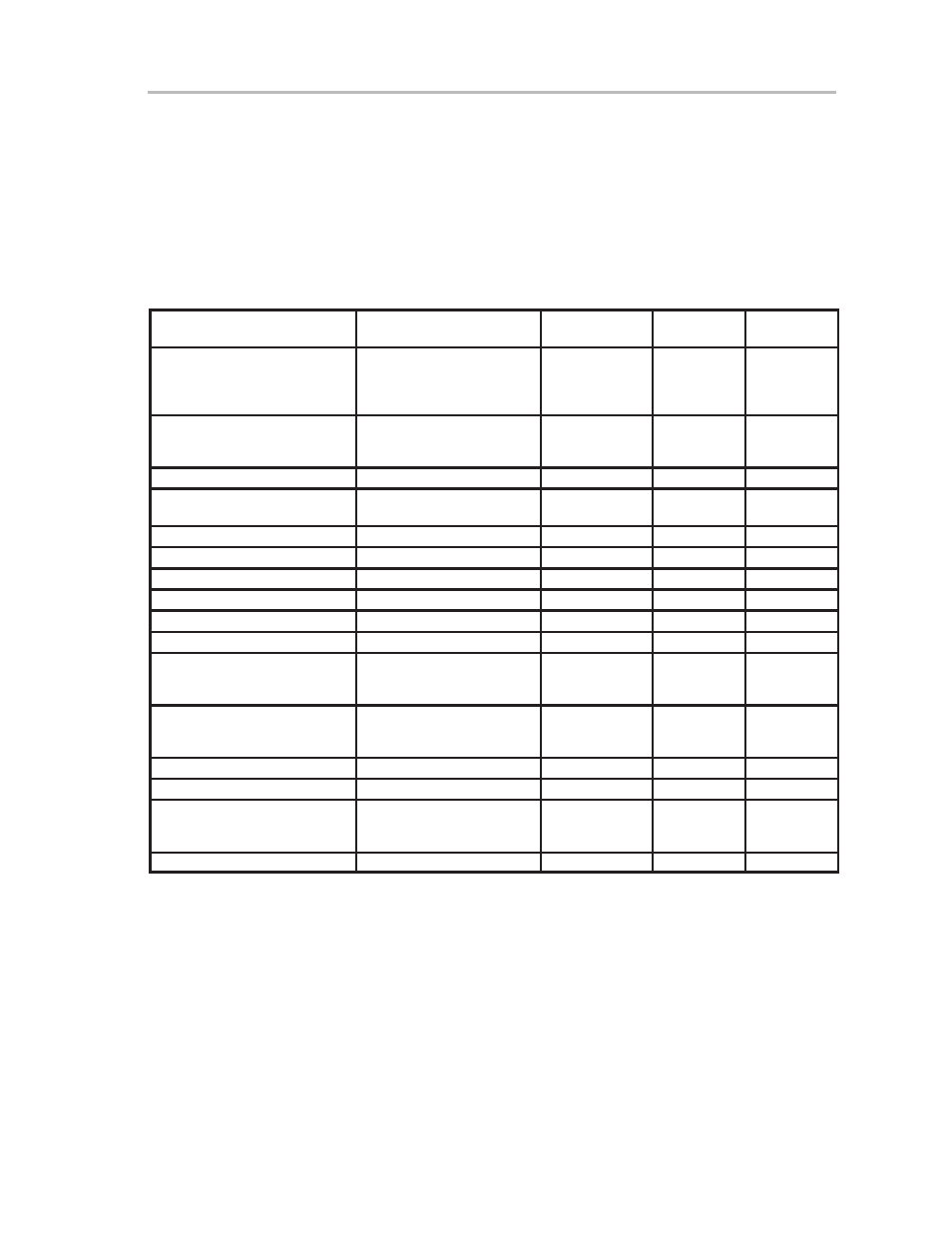

Table 3–5. Interrupt Sources, Flags, and Vectors of 14x Configurations

INTERRUPT SOURCE

INTERRUPT FLAG

SYSTEM

INTERRUPT

WORD

ADDRESS

PRIORITY

Power-up

External Reset

Watchdog

Flash memory

WDTIFG

KEYV

(see Note 1)

Reset

0FFFEh

15, highest

NMI

Oscillator Fault

Flash memory access violation

NMIIFG (see Notes 1 & 3)

OFIFG (see Notes 1 & 3)

ACCVIFG (see Notes 1 & 3)

(Non)maskable

(Non)maskable

(Non)maskable

0FFFCh

14

Timer_B7

BCCIFG0 (see Note 2)

Maskable

0FFFAh

13

Timer_B7

BCCIFG1 to BCCIFG6

TBIFG (see Notes 1 & 2)

Maskable

0FFF8h

12

Comparator_A

CMPAIFG

Maskable

0FFF6h

11

Watchdog timer

WDTIFG

Maskable

0FFF4h

10

USART0 receive

URXIFG0

Maskable

0FFF2h

9

USART0 transmit

UTXIFG0

Maskable

0FFF0h

8

ADC

ADCIFG (see Notes 1 & 2)

Maskable

0FFEEh

7

Timer_A3

CCIFG0 (see Note 2)

Maskable

0FFECh

6

Timer_A3

CCIFG1,

CCIFG2,

TAIFG (see Notes 1 & 2)

Maskable

0FFEAh

5

I/O port P1 (eight flags)

P1IFG.0 (see Notes 1 & 2)

To

P1IFG.7 (see Notes 1 & 2)

Maskable

0FFE8h

4

USART1 receive

URXIFG1

Maskable

0FFE6h

3

USART1 transmit

UTXIFG1

0FFE4h

2

I/O port P2 (eight flags)

P2IFG.0 (see Notes 1 & 2)

To

P2IFG.7 (see Notes 1 & 2)

Maskable

0FFE2h

1

0FFE0h

0, lowest

NOTES:

1. Multiple source flags

2. Interrupt flags are located in the module.

3. (Non)maskable: the individual interrupt-enable bit can disable an interrupt event, but the general-interrupt enable

can not disable it.

Note:

Some MSP430 devices have different implementations, See device datasheet for details.

3.4.2.1

External Interrupts

All eight bits of ports P1 and P2 are designed for interrupt processing of

external events. All individual I/O bits are independently programmable. Any

combinations of inputs, outputs, and interrupt conditions are possible. This

allows easy adaptation to different I/O configurations. See Chapter I/O Ports

for more details on I/O ports.