Texas Instruments MSP430x1xx User Manual

Page 427

Flash Memory Control Registers

C-15

Flash Memory

C.3.2 Flash Memory Control Register FCTL2

A PUC resets the flash timing generator. The generator is also reset if the

emergency exit bit EMEX is set.

The timing generator generates the timing necessary to write, erase, and

mass-erase from a selected clock source. Two control bits SSEL0 and SSEL1

in control register FCTL2 can select one of three clock sources. The clock

source selected should be divided to meet the frequency requirements for f

x

,

as specified in the device’s data sheet.

Writing to control register FCTL2 should not be attempted if the BUSY bit is set;

otherwise an access violation will occur (ACCVIFG=1). Read access to FCTL2

is possible at any time without restrictions.

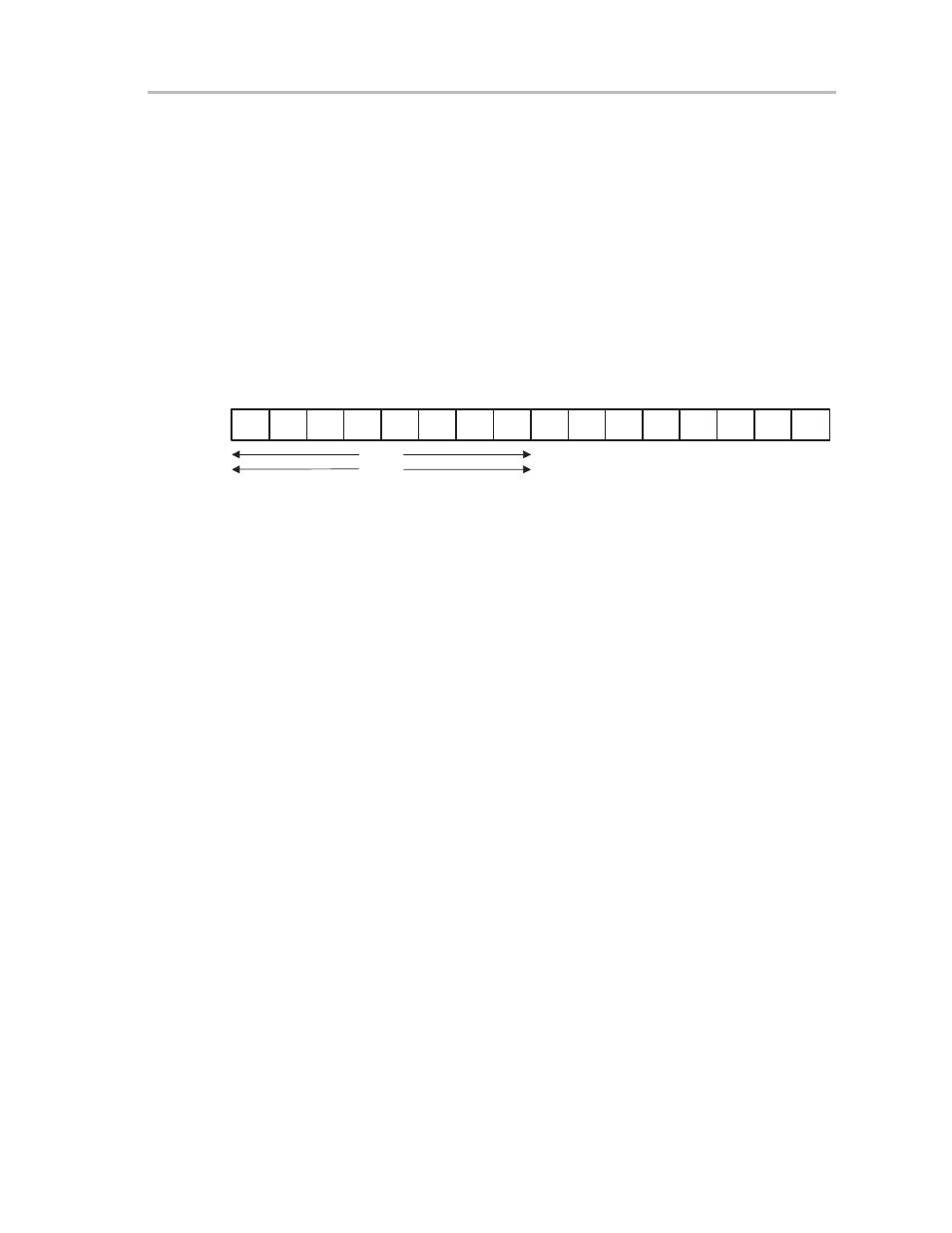

7

0

rw–0 rw–1 rw–0 rw–0 rw–0 rw–0 rw–1 rw–0

012Ah

FCTL2

SSEL1

15

8

FCTL2 read:

FCTL2 write:

0 9 6 h

0 A 5 h

SSEL0 FN5

FN4

FN3

FN2

FN1

FN0

The control bits are:

FN0

to

012Ah, bit0,

These six bits define the division rate of the clock signal. The division

rate can be 1 to 64, depending on the digital value of FN5 to FN0

FN5

012Ah, bit5,

plus one

SSEL0

012Ah, bit0,

Determine the clock source.

SSEL1

0:

ACLK

1:

MCLK

2,3 SMCLK