2 addressing modes – Texas Instruments MSP430x1xx User Manual

Page 71

Addressing Modes

5-7

16-Bit CPU

5.2

Addressing Modes

All seven addressing modes for the source operand and all four addressing

modes for the destination operand can address the complete address space.

The bit numbers in Table 5–4 describe the contents of the As and Ad mode bits.

See Section 5.3 for a description of the source address As and the destination

address Ad bits.

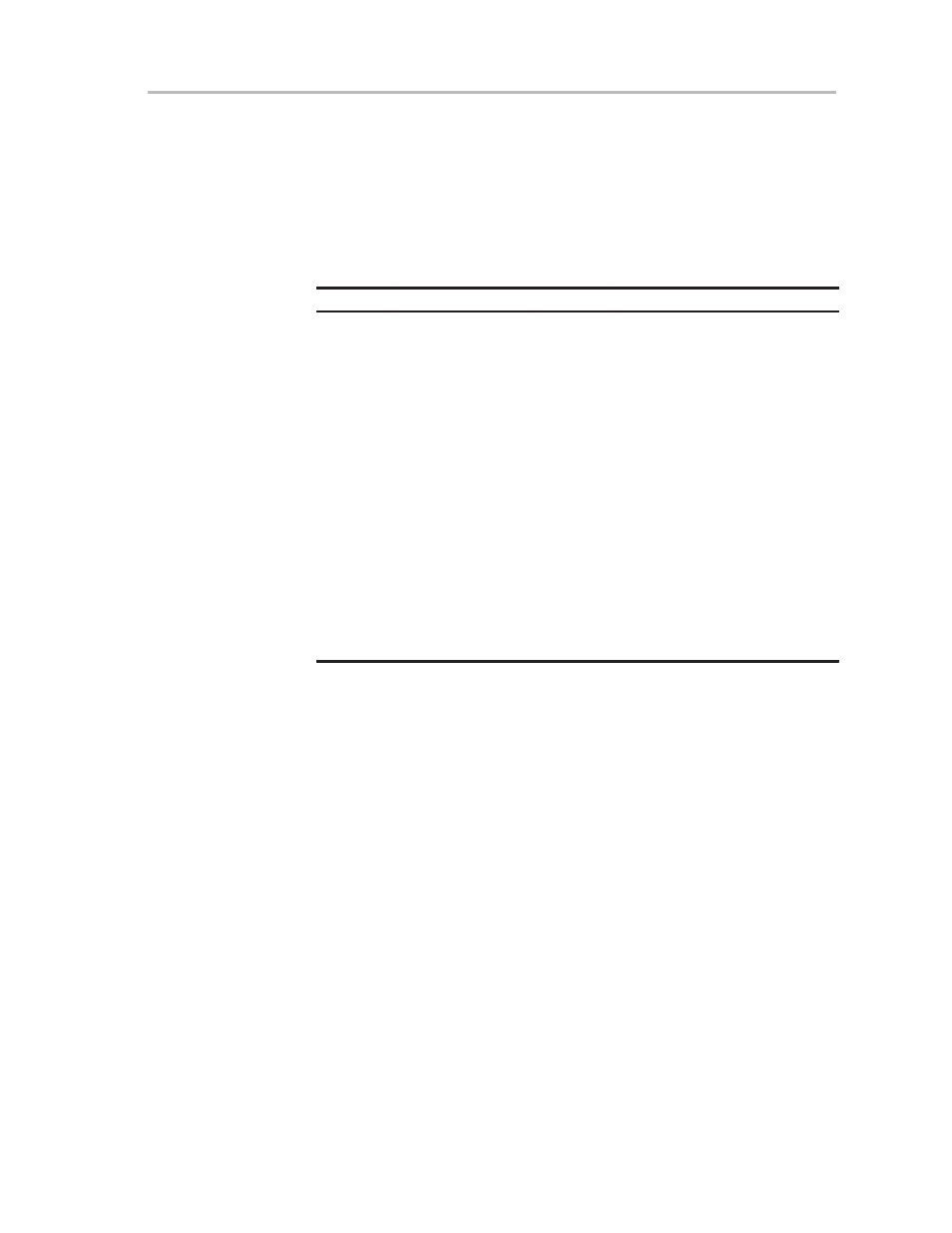

Table 5–4. Source/Destination Operand Addressing Modes

As/Ad

Addressing Mode

Syntax

Description

00/0

Register mode

Rn

Register contents are operand

01/1

Indexed mode

X(Rn)

(Rn + X) points to the operand

X is stored in the next word

01/1

Symbolic mode

ADDR

(PC + X) points to the operand

X is stored in the next word.

Indexed mode X(PC) is used.

01/1

Absolute mode

&ADDR

The word following the instruction

contains the absolute address.

10/–

Indirect register

mode

@Rn

Rn is used as a pointer to the

operand.

11/–

Indirect

autoincrement

@Rn+

Rn is used as a pointer to the

operand. Rn is incremented

afterwards.

11/–

Immediate mode

#N

The word following the instruction

contains the immediate constant

N. Indirect autoincrement mode

@PC+ is used.

The seven addressing modes are explained in detail in the following sections.

Most of the examples show the same addressing mode for the source and

destination, but any valid combination of source and destination addressing

modes is possible in an instruction.