Texas Instruments MSP430x1xx User Manual

Page 354

Instruction Set Overview

B-4

B.1.1 Instruction Formats

The following sections describe the instruction formats.

B.1.1.1 Double-Operand Instructions (Core Instructions)

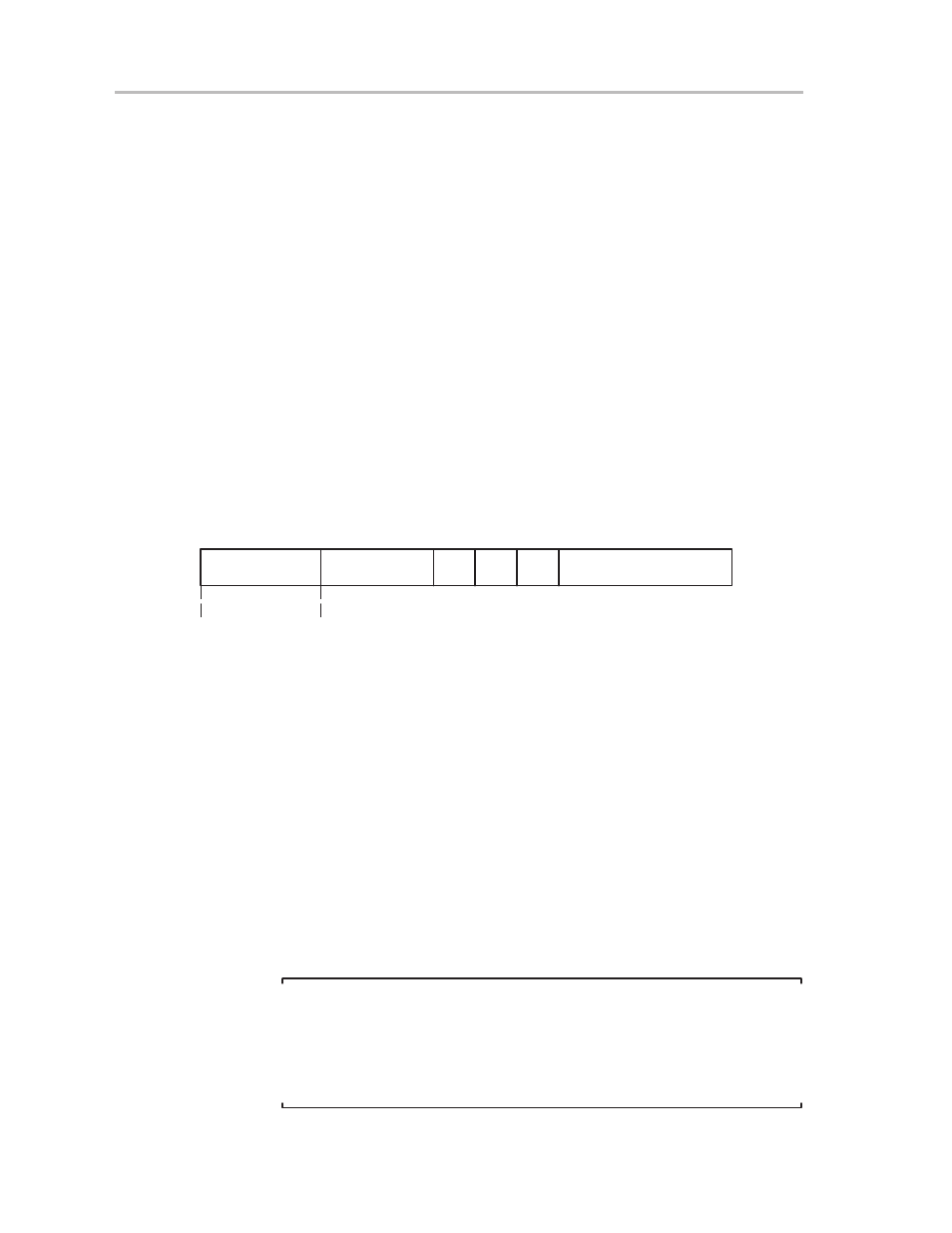

The instruction format using double operands, as shown in Figure B–1,

consists of four main fields to form a 16-bit code:

-

operational code field, four bits [op-code]

-

source field, six bits

[source register + As]

-

byte operation identifier, one bit [BW]

-

destination field, five bits

[dest. register + Ad]

The source field is composed of two addressing bits and a four-bit register

number (0....15). The destination field is composed of one addressing bit and

a four-bit register number (0....15). The byte identifier B/W indicates whether

the instruction is executed as a byte (B/W = 1) or as a word instruction

(B/W = 0).

Figure B–1.Double-Operand Instructions

As

Destination Register

Operational Code

Field

15

0

OP-Code

B/W

Ad

8

7

12 11

Source Register

6

5

4

3

Status Bits

V N Z C

ADD[.W];

ADD.B

src,dst

src + dst –> dst

*

*

*

*

ADDC[.W]; ADDC.B src,dst

src + dst + C –> dst

*

*

*

*

AND[.W];

AND.B

src,dst

src .and. dst –> dst

0 *

*

*

BIC[.W];

BIC.B

src,dst

.not.src .and. dst –> dst

–

–

– –

BIS[.W];

BIS.B

src,dst

src .or. dst –> dst

–

–

– –

BIT[.W];

BIT.B

src,dst

src .and. dst

0 *

*

*

CMP[.W];

CMP.B

src,dst

dst – src

*

*

*

*

DADD[.W]; DADD.B src,dst

src + dst + C –> dst (dec)

*

*

*

*

MOV[.W];

MOV.B

src,dst

src –> dst

– –

– –

SUB[.W];

SUB.B

src,dst

dst + .not.src + 1 –> dst

*

*

*

*

SUBC[.W]; SUBC.B src,dst

dst + .not.src + C –> dst

*

*

*

*

XOR[.W];

XOR.B

src,dst

src .xor. dst –> dst

*

*

*

*

Note:

Operations Using the Status Register (SR) for Destination

All operations using status register SR for destination overwrite the SR

contents with the operation result; as described in that operation, the status

bits are not affected.

Example: ADD #3,SR ; Operation: (SR) + 3 ––> SR