1 cpu registers – Texas Instruments MSP430x1xx User Manual

Page 66

CPU Registers

5-2

5.1

CPU Registers

Sixteen 16-bit registers (R0, R1, and R4 to R15) are used for data and

addresses and are implemented in the CPU. They can address up to

64 Kbytes (ROM, RAM, peripherals, etc.) without any segmentation. The

complete CPU-register set is described in Table 5–1. Registers R0, R1, R2,

and R3 have dedicated functions, which are described in detail later.

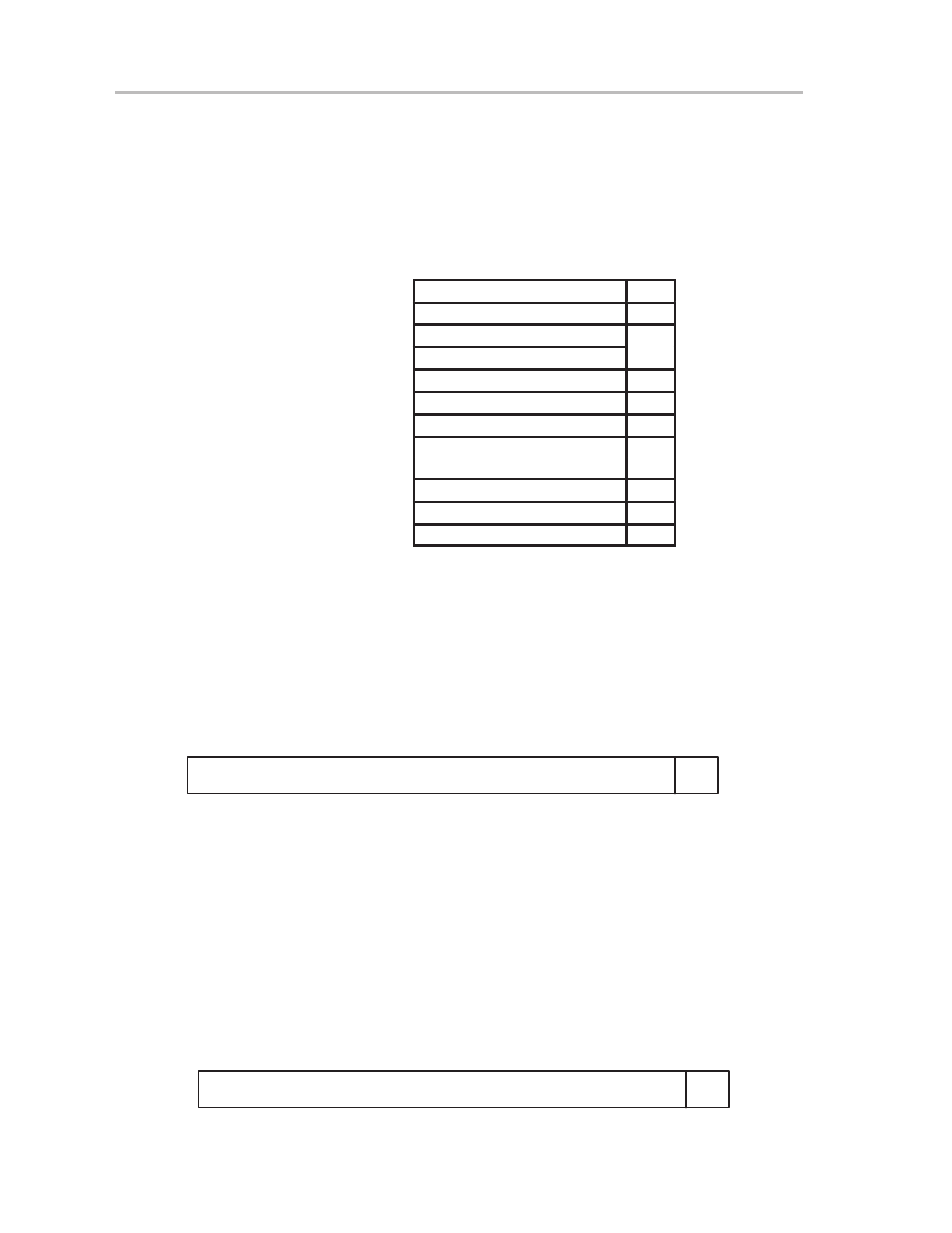

Table 5–1. Register by Functions

Program counter (PC)

R0

Stack pointer (SP)

R1

Status register (SR)

R2

Constant generator (CG1)

R2

Constant generator (CG2)

R3

Working register R4

R4

Working register R5

R5

:

:

:

:

Working register R13

R13

Working register R14

R14

Working register R15

R15

5.1.1

The Program Counter (PC)

The 16-bit program counter points to the next instruction to be executed. Each

instruction uses an even number of bytes (two, four, or six), and the program

counter is incremented accordingly. Instruction accesses are performed on

word boundaries, and the program counter is aligned to even addresses.

Figure 5–1 shows the program counter bits.

Figure 5–1. Program Counter

0

15

0

Program Counter Bits 15 to 1

1

5.1.2

The System Stack Pointer (SP)

The system stack pointer must always be aligned to even addresses because

the stack is accessed with word data during an interrupt request service. The

system SP is used by the CPU to store the return addresses of subroutine calls

and interrupts. It uses a predecrement, postincrement scheme. The

advantage of this scheme is that the item on the top of the stack is available.

The SP can be used by the user software (PUSH and POP instructions), but

the user should remember that the CPU also uses the SP. Figure 5–2 shows

the system SP bits.

Figure 5–2. System Stack Pointer

0

15

0

System Stack Pointer Bits 15 to 1

1