Texas Instruments MSP430x1xx User Manual

Page 432

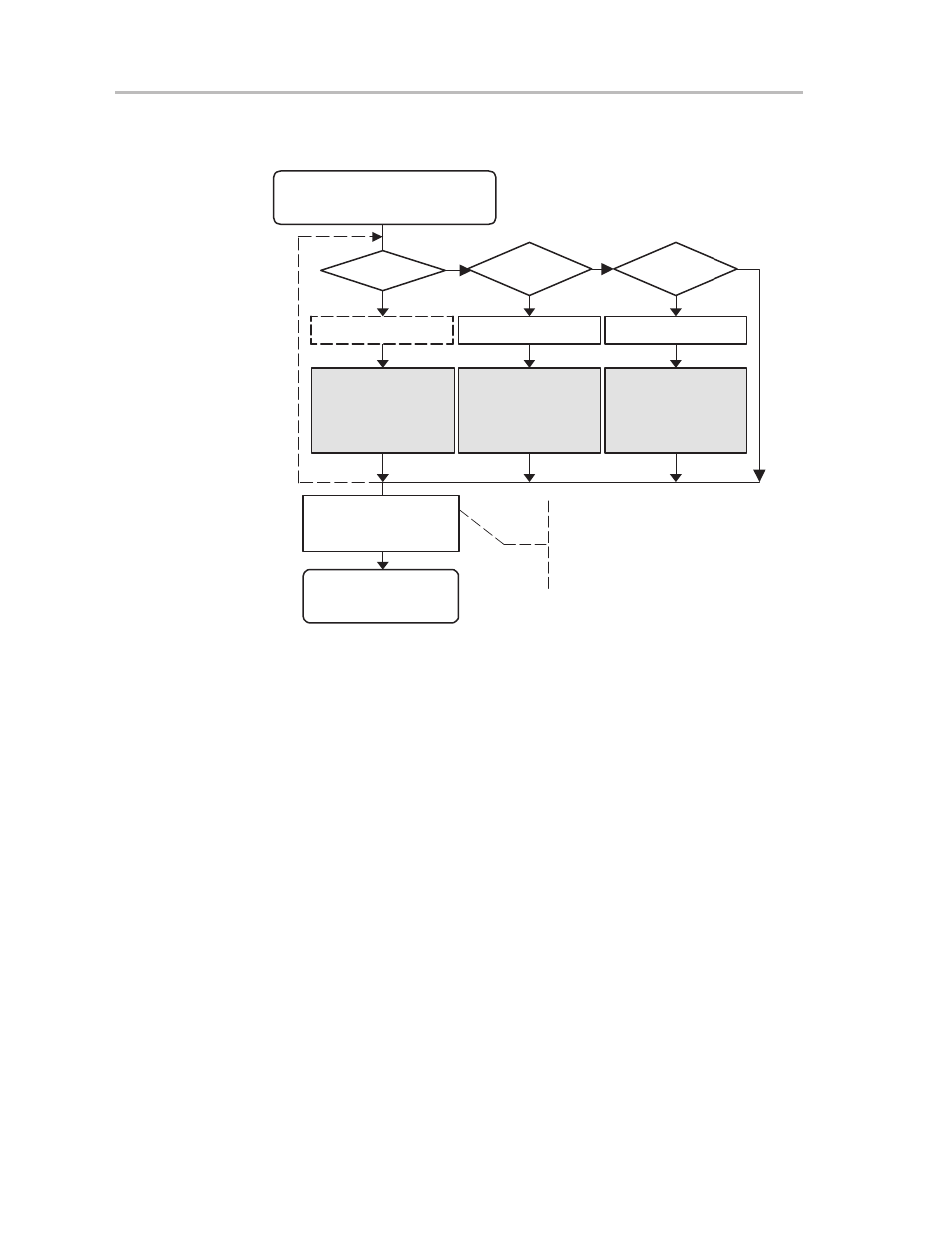

Flash Memory, Interrupt and Security Key Violation

C-20

C.4.1 Example of an NMI Interrupt Handler

yes

no

OFIFG=1

yes

no

ACCVIFG=1

yes

Reset ACCVIFG

no

NMIIFG=1

Reset NMIIFG

Example1:

BIS #(NMIIE+OFIE+ACCVIE), &IE1

Example2:

BIS Mask,&IE1 ; Mask enables only

; interrupt sources

Reset OFIFG

Start of NMI Interrupt Handler

Reset by HW:

OFIE, NMIE, NMIIFG

User’s Software,

Oscillator Fault

Handler

User’s Software,

Flash Access

Violation Handler

User’s Software,

External NMI

Handler

Optional

Set NMIIE, OFIE,

ACCVIE Within One

Instruction

RETI

End of NMI Interrupt

Handler

The NMI handler takes care of all sources requesting a nonmaskable interrupt.

The NMI interrupt is a multiple-source interrupt per MSP430 definition. The

hardware resets the interrupt-enable flags: the external nonmaskable interrupt

enable NMIIE, the oscillator fault interrupt enable OFIE, and the flash memory

access-violation interrupt enable. The individual software handlers reset the

interrupt flags and reenables the interrupt enable bits according to the applica-

tion needs. After all software is processed, the interrupt enable bits have to be

set if another NMI event is to be accepted. Setting the interrupt enable bits

should be the last instruction before the return-from-interrupt instruction RETI.

If this rule is violated, the stack can grow out of control while other NMI re-

quests are already pending. Setting the interrupt enable bits can be accom-

plished by using a bit-set-instruction BIS using immediate data or a mask. The

mask data can be modified anywhere via software (for example in RAM); this

constitutes the nonmaskable interrupt processing.

C.4.2

Protecting One-Flash Memory-Module Systems From Corruption

MSP430 configurations having one flash memory module use this module for

program code and interrupt vectors. When the flash memory module is in a

write, erase, or mass-erase operation and the program accesses it, an access

violation occurs. This violation will request an interrupt service – but when the

interrupt vector is read from the flash memory, 03FFFh will be read indepen-

dent of the data in the flash memory at the vector’s memory location.