Texas Instruments MSP430x1xx User Manual

Page 198

T

imer Modes

1

1-22

T

imer_B

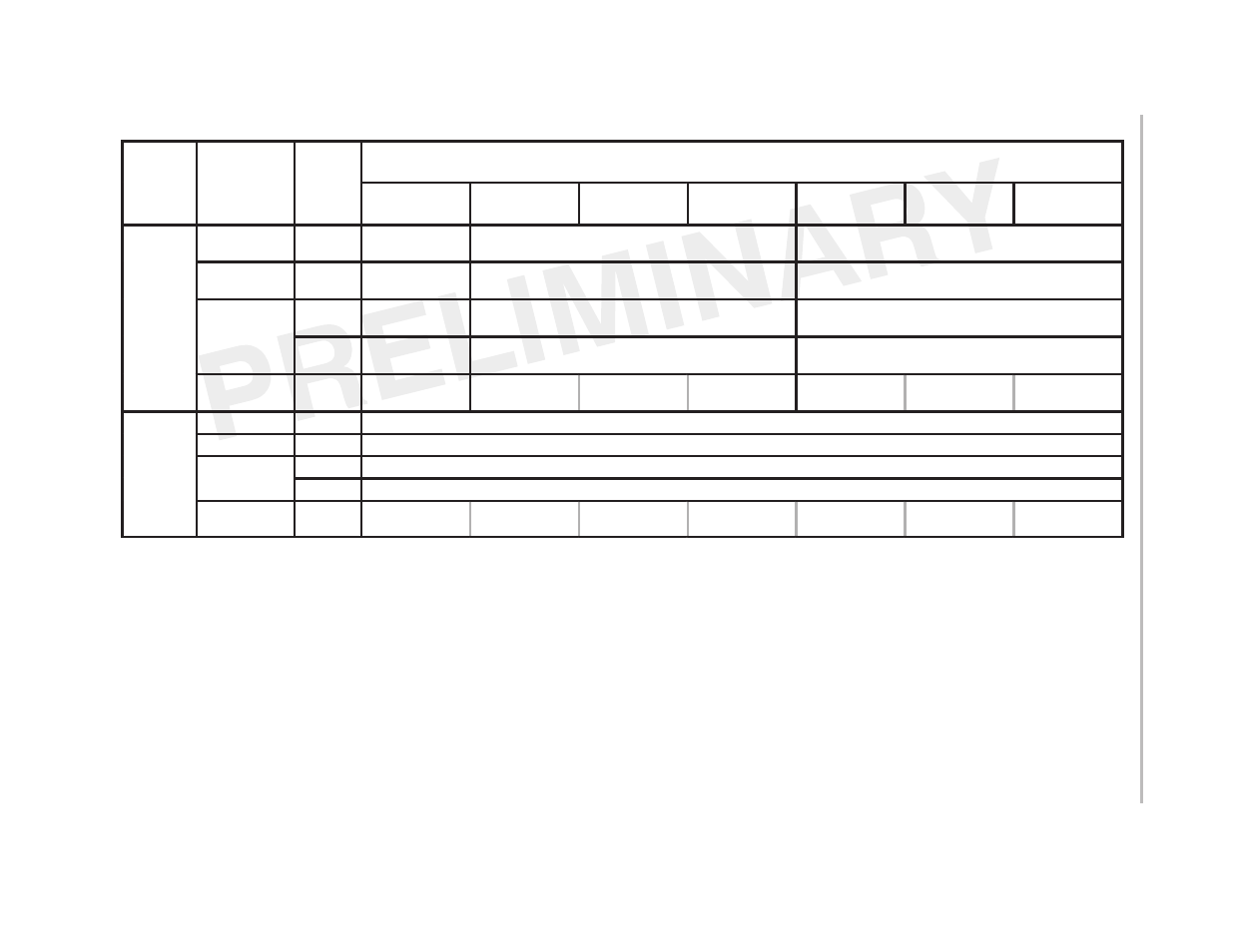

Table 11–2. Shadow Register Operating Modes (Continued)

TBCLGRP

CLLDx From

Lowest

CCTLx in

Counter

Mode

Load Conditions

TBCLGRP

CCTLx in

Group (see

Note 1)

Mode

MCx

0

1

2

3

4

5

6

0

0–3

Immediate

TBCL1, TBCL2, TBCL3 loaded immediately when the

corresponding CCRx register is loaded

TBCL4, TBCL5, TBCL6 loaded immediately when the

corresponding CCRx register is loaded

1

1–3

TBR counts to 0

TBCL1, TBCL2, TBCL3 updated simultaneously when

TBR counts to 0

TBCL4, TBCL5, TBCL6 updated simultaneously when

TBR counts to 0

2

2

1,2

TBR counts to 0

TBCL1, TBCL2, TBCL3 updated simultaneously when

TBR counts to 0

TBCL4, TBCL5, TBCL6 updated simultaneously when

TBR counts to 0

2

3

TBR counts to 0

or to TBCL0

TBCL1, TBCL2, TBCL3 updated simultaneously when

TBR counts to 0 or to TBCL0

TBCL4, TBCL5, TBCL6 updated simultaneously when

TBR counts to 0 or to TBCL0

3

1–3

TBR counts to

TBCL0

TBR counts to

TBCL1

TBR counts to

TBCL2

TBR counts to

TBCL3

TBR counts to

TBCL4

TBR counts to

TBCL5

TBR counts to

TBCL6

0

0–3

TBCL0, TBCL1, TBCL2, TBCL3, TBCL4, TBCL5, TBCL6 Loaded immediately when the corresponging CCRx register is loaded.

1

1–3

TBCL0,TBCL1, TBCL2, TBCL3, TBCL4, TBCL5, TBCL6 updated simultaneously when TBR counts to 0

3

2

1,2

TBCL0,TBCL1, TBCL2, TBCL3, TBCL4, TBCL5, TBCL6 updated simultaneously when TBR counts to 0

3

2

3

TBCL0,TBCL1, TBCL2, TBCL3, TBCL4, TBCL5, TBCL6 updated simultaneously when TBR counts to 0 or to TBCL0

3

1–3

TBR counts to

TBCL0

TBR counts to

TBCL1

TBR counts to

TBCL2

TBR counts to

TBCL3

TBR counts to

TBCL4

TBR counts to

TBCL5

TBR counts to

TBCL6

Notes:

1) When using groups, load mode for the group is selected with the CLLDx bits of the lowest numbered CCTLx register in the group (except when TBCLGRP=3). For example,

when grouped by 2, the CLLDx bits of CCTL3 determine the load mode for TBCL3 and TBCL4. When grouped by 3, the CLLDx bits of CCTL4 determine the load mode for

TBCL4, TBCL5, and TBCL6, etc. When TBCLGRP=3 the CLLDx bits from TBCTL1 are used.

2) When using groups, all CCRx registers must be updated with new data before the load will take place (except when using immediate mode), even if new data = old data.

When using immediate mode, each compare latch is updated immediately when its corresponding CCRx register is updated.

3) When using groups, different load modes may be selected for each group. For example, when grouped by 3, immediate mode may be selected (via CLLDx bits in CCTL1)

for TBCL1, TBCL2, and TBCL3, and mode 2 may be selected (via CLLDx bits in CCTL4) for TBCL4, TBCL5, and TBCL6.