Texas Instruments MSP430x1xx User Manual

Page 131

Ports P3, P4, P5, P6

8-11

Digital I/O Configuration

8.3.1.4

Function Select Registers PnSEL

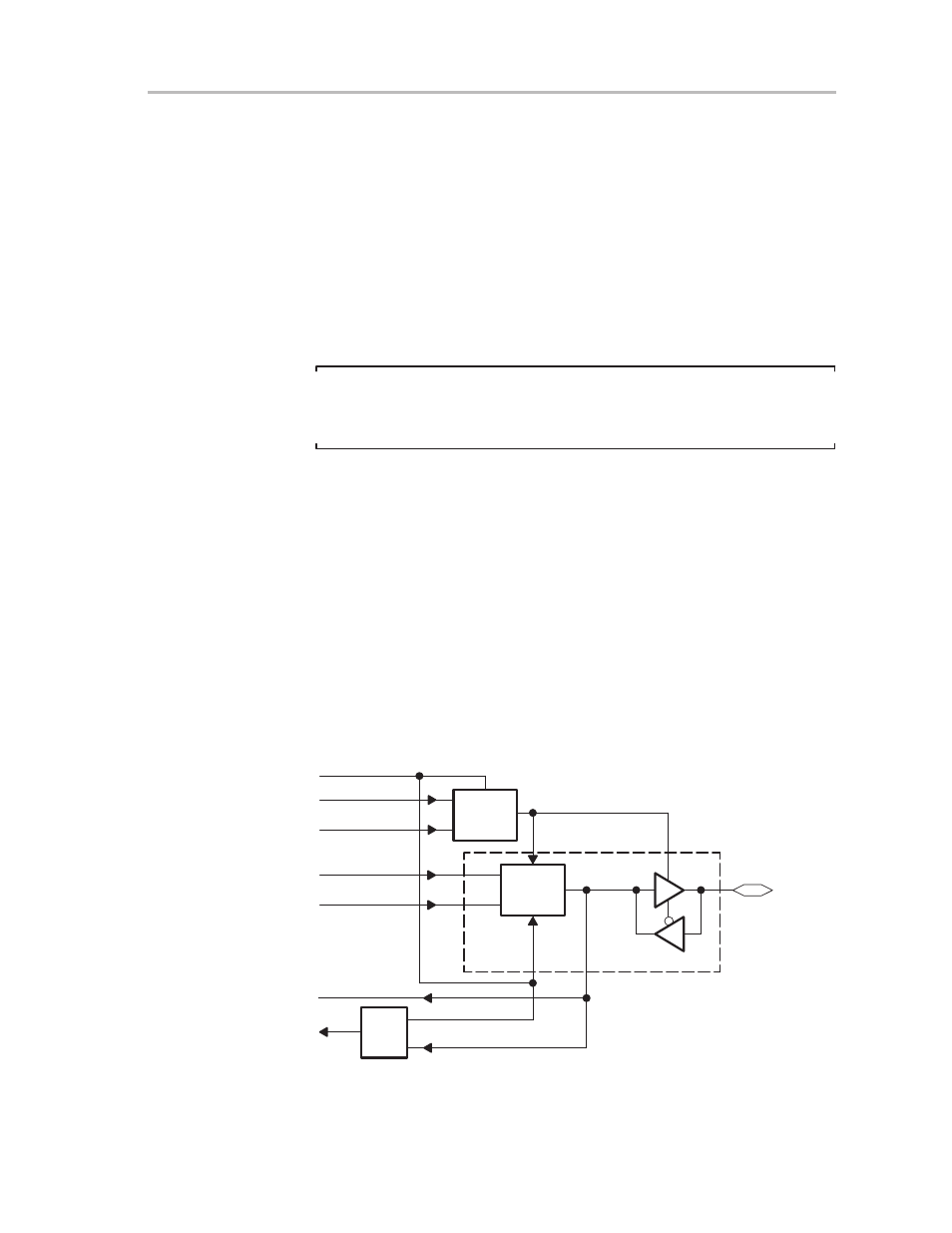

Ports P3–P6 pins are often multiplexed with other peripheral modules to

reduce overall pin count on MSP430 devices (see the specific device data

sheet to determine which other peripherals also use the device pins). Control

registers PnSEL are used to select the desired pin function—I/O port or other

peripheral module. Each register contains eight bits corresponding to each

pin, and each pin’s function is individually selectable. All bits in these registers

are reset by the PUC signal. The bit definitions are:

Bit = 0: Port function is selected for the pin

Bit = 1: Other peripheral module function is selected for the pin

Note:

Function Select With PnSEL Registers

The interrupt-edge-select circuitry is disabled if control bit PnSEL.x is set.

Therefore, the input signal can no longer generate an interrupt.

When a port pin is selected to be used as an input to a peripheral module other

than the I/O port (PnSEL.x=1), the actual input signal to the peripheral module

is a latched representation of the signal at the device pin (see Figure 8–4

schematic). The latch uses the PnSEL.x bit as its enable, so while PnSEL.x=1,

the internal input signal simply follows the signal at the pin. However, if the

PnSEL.x bit is reset, then the output of the latch (and therefore the input to the

other peripheral module) represents the value of signal at the device pin, just

prior to the bit being reset.

8.3.2

Port P3–P6 Schematic

The pin logic of each individual port signal is shown in Figure 8–4.

Figure 8–4. Schematic of Bits Pn.x

Pad Logic

Pn.x

Output

MUX

Output

MUX

PnIN.x

PnSEL.x

PnDIR.x

EN

A

Y

Module x IN

Module x OUT

PnOUT.x

Direction Control

From Module

n = 3 for Port3, 4 for Port P4, 5 for Port P5, and 6 for Port P6

x = 0 to 7, according to bits 0 to 7