Texas Instruments MSP430x1xx User Manual

Page 355

Instruction Set Overview

B-5

Instruction Set Description

B.1.1.2 Single Operand Instructions (Core Instructions)

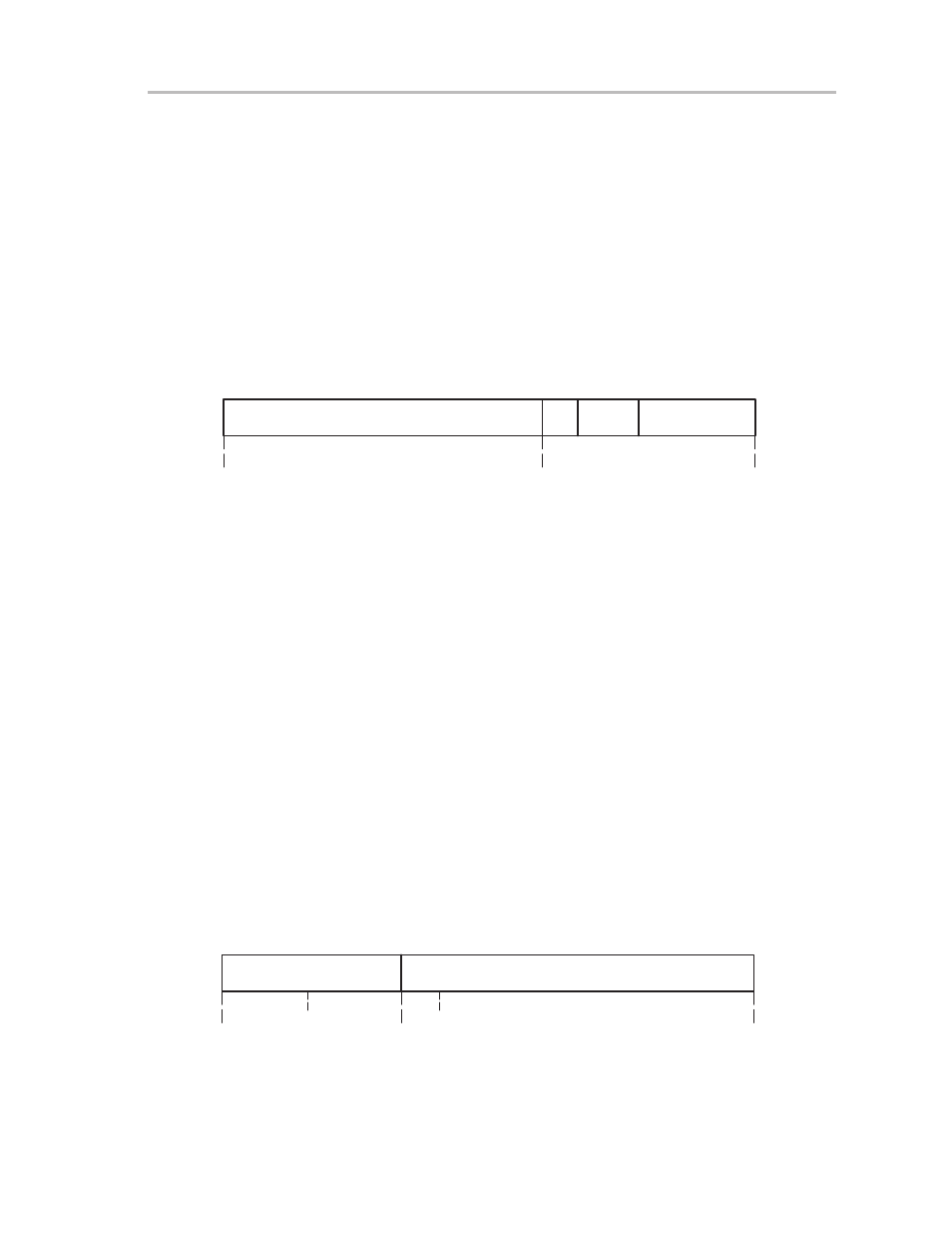

The instruction format using a single operand, as shown in Figure B–2,

consists of two main fields to form a 16-bit code:

-

operational code field, nine bits with four MSBs equal to 1h

-

byte operation identifier, one bit

[B/W]

-

destination field, six bits

[destination register + Ad]

The destination field is composed of two addressing bits and the four-bit

register number (0....15). The destination field bit position is the same as that

of the two operand instructions. The byte identifier (B/W) indicates whether the

instruction is executed as a byte (B/W = 1) or as a word (B/W = 0).

Figure B–2.Single-Operand Instructions

B/W

Destination Register

15

0

0

9

7

12

11

6

5

4

3

0

0

1

X

X

X

X

X

Ad

10

Destination Field

Operational Code Field

Status Bits

V N Z C

RRA[.W];

RRA.B

dst

MSB

→

MSB ...LSB

→

C

0 *

*

*

RRC[.W];

RRC.B

dst

C

→

MSB ........LSB

→

C

*

*

*

*

PUSH[.W]; PUSH.B

dst

SP – 2

→

SP, src

→

@SP

– –

– –

SWPB

dst

swap bytes

– –

– –

CALL

dst

PC

→

2 + @SP, dst

→

PC

– –

– –

RETI

dst

TOS

→

SR, SP + 2

→

SP

*

*

*

*

TOS

→

PC, SP + 2

→

SP

SXT

dst

Bit 7

→

Bit 8 ........ Bit 15

0 *

*

*

B.1.2 Conditional and Unconditional Jumps (Core Instructions)

The instruction format for conditional and unconditional jumps, as shown in

Figure B–3, consists of two main fields to form a 16-bit code:

-

operational code (op-code) field, six bits

-

jump offset field, ten bits

The operational-code field is composed of the op-code ( three bits), and three

bits according to the following conditions.

Figure B–3.Conditional and Unconditional Jump Instructions

15

0

9

12

13

0

0

1

X

X

X

X

X

10

Operational Code Field

X

X

X

X

X

X

X

X

OP-Code

Jump-On Code

Sign

Offset

Jump Offset Field

Conditional jumps jump to addresses in the range of –511 to +512 words

relative to the current address. The assembler computes the signed offsets

and inserts them into the op-code.