Texas Instruments MSP430x1xx User Manual

Page 245

Baud Rate Considerations

12-29

USART Peripheral Interface, UART Mode

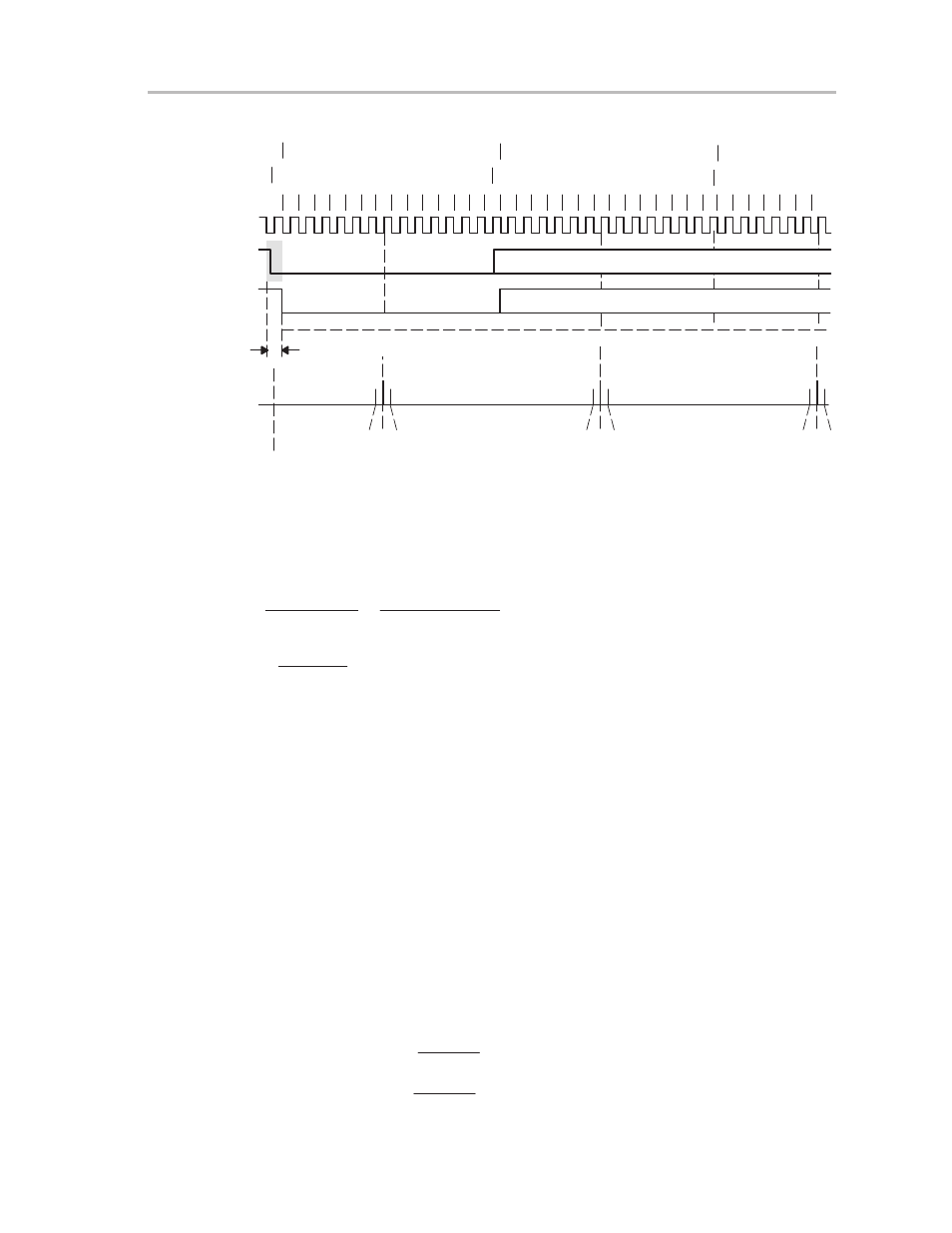

Figure 12–29. Synchronization Error

1 2 3

4 5 6

0

i

t0

t

target

7 8

1

t1

2

9 10 11 12 13 14 1 2 3

4 5 6 7 8

9 10 11 12 13 14 1 2 3

4 5 6 7

t0

t1

t2

ST

D0

D2

D0

D2

ST

Synchronization Error

±

0.5x BLSCLK

Int(UBR/2)+m0 =

Int (13/2)+1 = 6+1 = 7

Majority Vote Taken

Majority Vote Taken

UBR +m1 = 13+1 = 14

UBR +m2 = 13+0 = 13

Majority Vote Taken

BRSCLK

URXD

URXDS

t

actual

Sample

URXDS

The target start-bit detection-baud-rate timing t

target(0)

is half the baud-rate

timing t

baud rate

because the bit is tested in the middle of its period. The target

baud rate timing t

targeti

for all of the other succeeding bits is the baud rate timing

t

baud rate

.

Error [%]

+

ǒ

baud rate

BRCLK

NJ

2

ƪ

m0

)

int

ǒ

UBR

ń

2

Ǔ

ƫ

)

ǒ

i

UBR

) S

n–1

i

+

1

m

i

Ǔ

Nj

*

1

–i

Ǔ

100%

Error [%]

+

t

actual

0

)

t

target

0

0.5

t

target

0

)

S

n–1

i

+

1

t

actual

i

* S

n–1

i

+

1

t

target

i

t

target

i

100%

OR

Where:

baud rate is the required baud rate

BRCLK is the input frequency—selected for UCLK, ACLK, or SMCLK

i = 0 for the start bit, 1 for data bit D0, and so on

UBR is the division factor in registers UBR1 and BRB0

Example 12–4. Synchronization Error—2400 Baud

The following data are assumed:

Baud rate = 2400

BRCLK =

32,768 Hz (ACLK)

UBR =

13, since the ideal division factor is 13.67

m = 6Bh:

m7 = 0, m6 = 1, m5 = 1, m4 = 0, m3 = 1, m2 = 0, m1 = 1 and

m0 = 1

The LSB (m0) of the modulation register is used first.

Start bit Error [%]

+

ǒ

baud rate

BRCLK

[2x(1

)

6)

)

(0

UBR

)

0 –0)]–1

Ǔ

100%

+

2.54%

Data bit D0 Error [%]

+

ǒ

baud rate

BRCLK

[2x(1

)

6)

)

(1

UBR

)

1)]–1–1

Ǔ

100%

+

5.08%